Freescale Semiconductor MPC5200B User Manual

Page 535

MPC5200B Users Guide, Rev. 1

15-24

Freescale Semiconductor

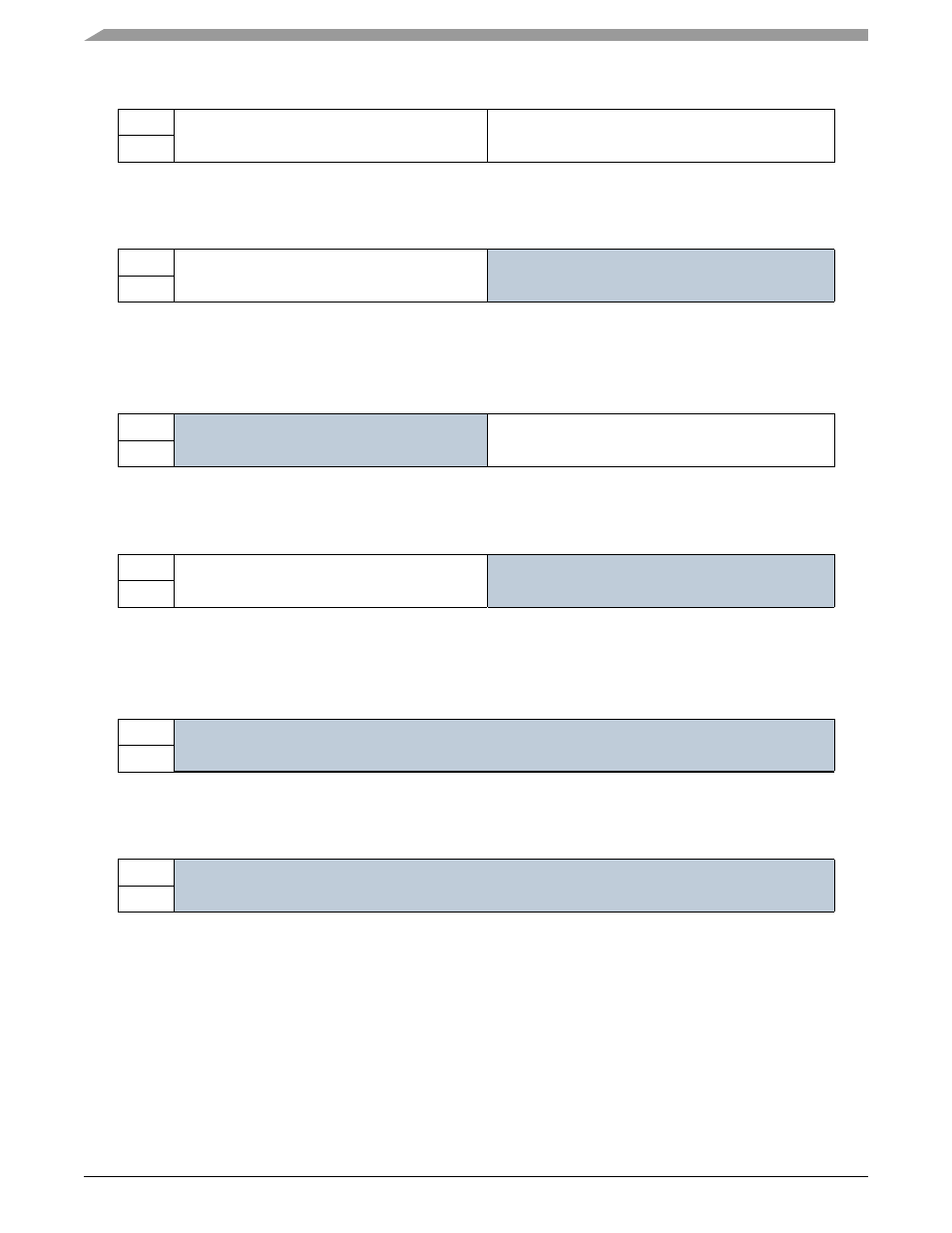

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

R

FrameSyncDiv[0:7]

BitClkDiv[8:15]

W

msb

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

BitClkDiv[0:7]

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-33. Codec Clock Register (0x20)—CCR for MIR/FIR Mode

msb

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

BitClkDiv[8:15]

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

msb

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

BitClkDiv[0:7]

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-34. Codec Clock Register (0x20)—CCR for other Modes

msb

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

msb

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-32. Codec Clock Register (0x20)—CCR for Codec Mode

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1