Freescale Semiconductor MPC5200B User Manual

Page 317

MPC5200B Users Guide, Rev. 1

10-20

Freescale Semiconductor

Registers

10.3.2.7

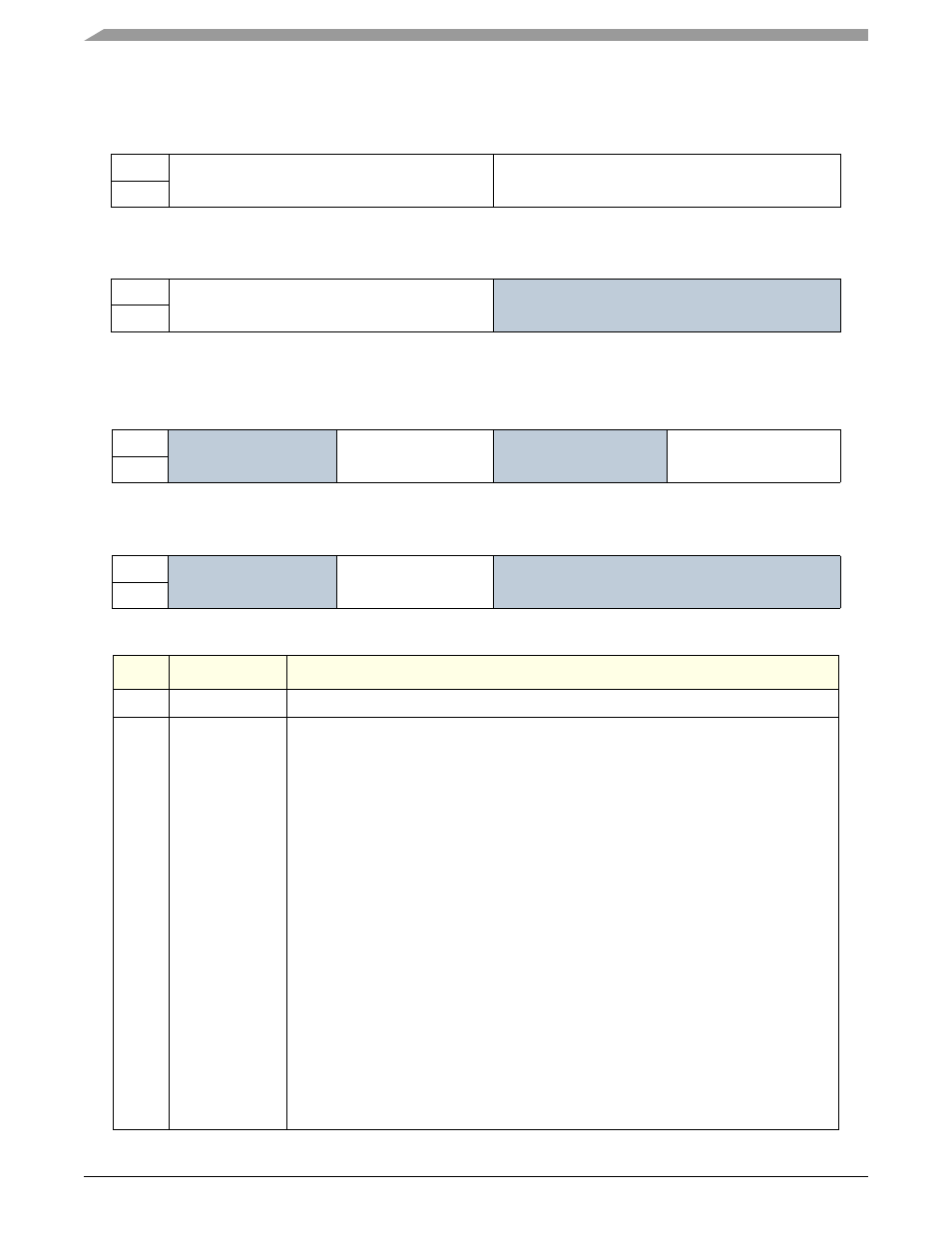

Initiator Window 2 Base/Translation Address Register PCIIW2BTAR(RW) —MBAR +

0x0D78

10.3.2.8

Initiator Window Configuration Register PCIIWCR(RW) —MBAR + 0x0D80

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Window 2 Base Address

Window 2 Address Mask

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Window 2 Translation Address

Reserved

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

Window 0

Control

Reserved

Window 1

Control

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

Window 2

Control

Reserved

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:3

Reserved

Reserved register. Write a zero to this register.

4:7

Window 0 Control

[3:0]

Bit[3] - IO/M#.

0 = Window is mapped to PCI memory

1 = Window is mapped to PCI I/O

Bit[2:1] - PCI Read Command (PRC).

If bit[3] is programmed memory, “0”, then these bits are used to determine the type of PCI

memory command to issue. See

. If bit[3] is set to “1”, the value of these bits

are meaningless.

00 = PCI Memory Read

01 = PCI Memory Read Line

10 = PCI Memory Read Multiple

11 = Reserved

Note: A PCI write command is automatically detected and needs not to be explicitly

configured. No PCI Write and Invalidate command is allowed in any case with this

interface.

Bit[0] - Enable.

This bit is set to indicate the address registers that control the XL Bus initiator interface

access to PCI initialized and will be used. The PCI Controller can begin to decode XL Bus

PCI accesses.

0 = Do not decode XL Bus PCI accesses to Window

1 = Registers initialized - decode accesses to Window