4 usb hc interrupt status register -mbar + 0x 100c, Usb hc interrupt status register —mbar + 0x100c -9, Usb hc interrupt status register -9 – Freescale Semiconductor MPC5200B User Manual

Page 412: Usb hc interrupt status register, 0x100c)

Host Control (HC) Operational Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

12-9

12.4.2.4

USB HC Interrupt Status Register —MBAR + 0x100C

This register provides status on various events that cause hardware interrupts. When an event occurs, HC sets the corresponding register bit.

When a bit is set, a hardware interrupt is generated, if the interrupt is enabled in the HcInterruptEnable register and the MasterInterruptEnable

bit is set. HCD may clear specific bits in this register by writing 1 to bit positions to be cleared. HCD may not set any of these bits. HC never

clears the bit.

29

BLF

BulkListFilled—bit indicates whether there are Bulk List TDs. HCD sets this bit when it adds

a TD to a Bulk List ED. When HC begins processing the Bulk List head, it checks BF.

•

If BLF is 0, HC does not start Bulk List processing.

•

If BLF is 1, HC starts Bulk List processing and sets BF to 0.

•

If HC finds a Bulk List TD, HC sets BLF to 1, causing Bulk List processing to continue.

•

If HC does not find a Bulk List TD and HCD does not set BLF, then BLF remains 0 when

HC completes processing and Bulk List processing stops.

30

CLF

ControlListFilled—bit indicates whether there are Control List TDs. HCD sets this bit when

it adds a TD to a Control List ED. When HC begins processing the Control List head, it checks

CLF.

•

If CLF is 0, HC does not start Control List processing.

•

If CF is 1, HC starts Control List processing and sets CLF to 0.

•

If HC finds a Control List TD, CLF is set to 1, causing Control List processing to continue.

•

If HC does not find a Control List TD and HCD does not set CLF, then CLF remains 0

when HC completes processing and Control List processing stops.

31

HCR

HostControllerReset—HCD sets bit to initiate a software reset of HC. Regardless of the HC

functional state, it moves to the USBSUSPEND state in which most of the operational

registers are reset except those stated otherwise. For example, HcControl Interrupt Routing

field and no Host bus access is allowed.

On completion of the reset operation, HC clears this bit. Completion must be within 10ms.

When set, this bit should not cause a root hub reset and no subsequent reset signaling

should be asserted to downstream ports.

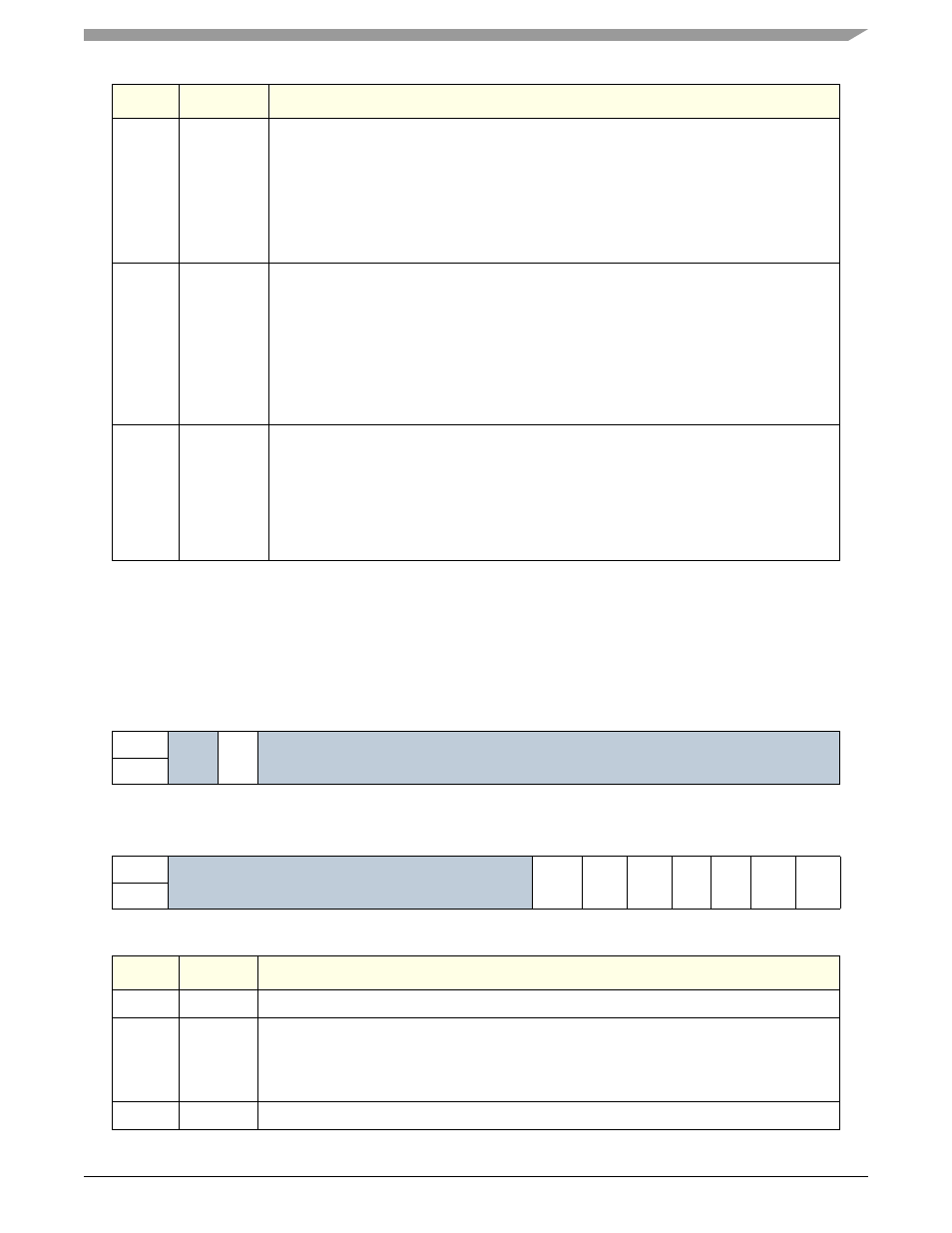

Table 12-4. USB HC Interrupt Status Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Rsvd

OC

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

RHSC

FNO

UE

RD

SF

WDH

SO

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0

—

Reserved

1

OC

OwnershipChange—HC sets this bit when HCD sets the HcCommandStatus

OwnershipChangeRequest field. This event, when unmasked, always generate an immediate

System Management Interrupt (SMI).

When the SMI pin is not implemented, the OC bit is tied to 0.

2:24

—

Reserved

Bits

Name

Description