1588 ptp interface signals – Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 90

External Time-of-Day Module for 1588 PTP Variations

Low Latency 40-100GbE IP cores that include the 1588 PTP module require an external time-of-day

(TOD) module to provide the current time-of-day in each clock cycle, based on the incoming clock. The

TOD module must update the time-of-day output value on every clock cycle, and must provide the TOD

value in the V2 format.

The example project you can generate for your IP core PTP variation includes two TOD modules, one for

the RX MAC and one for the TX MAC, and demonstrates their connections to the IP core.

Related Information

•

External Time-of-Day Module for Variations with 1588 PTP Feature

on page 2-20

•

Low Latency 40-100GbE IP Core Example Project

Altera provides an example Quartus II project with the Low Latency 40-100GbE IP core. This example

project can compile and configure on an Altera device. In addition, for Arria 10 IP core variations, you

can use this example project to view one option for connecting the external TX PLL or TX PLLs in your

design.

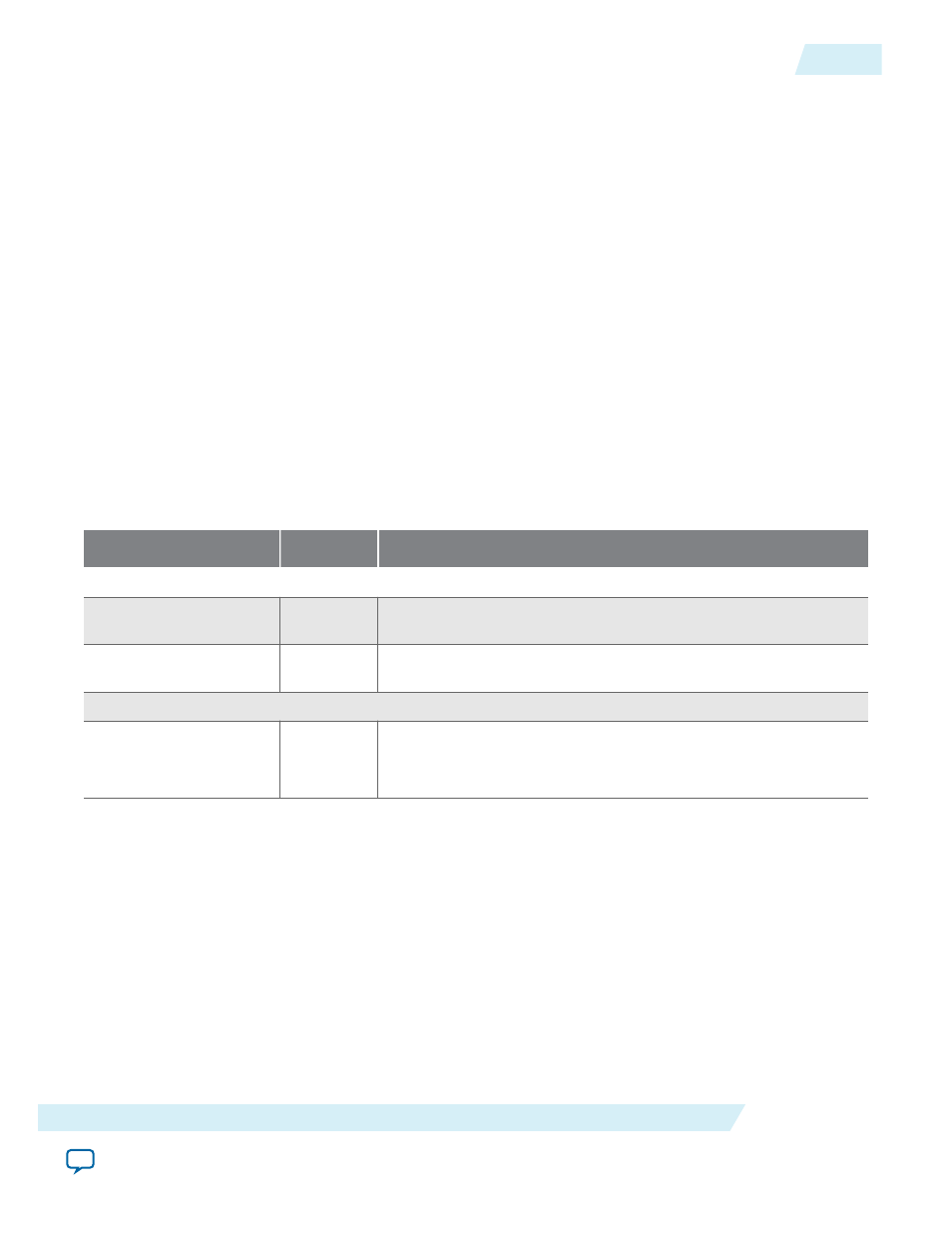

1588 PTP Interface Signals

Table 3-11: Signals of the 1588 Precision Time Protocol Interface

Signals are clocked by

clk_rxmac

or

clk_txmac

, as specified.

Signal Name

Direction

Description

PTP Interface to TOD module

tod_txmac_in[95:0]

Input

Current timestamp in

clk_txmac

clock domain. Connect this

signal to the external TOD module.

tod_rxmac_in[95:0]

Input

Current timestamp in

clk_rxmac

clock domain. Connect this

signal to the external TOD module.

PTP Interface to Client

tx_in_ptp

Input

Indicates the current packet on the TX client interface is a 1588

PTP packet. TX client must assert and deassert this signal

synchronously with the TX SOP signal for 1588 PTP packets.

UG-01172

2015.05.04

External Time-of-Day Module for 1588 PTP Variations

3-45

Functional Description

Altera Corporation