Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 120

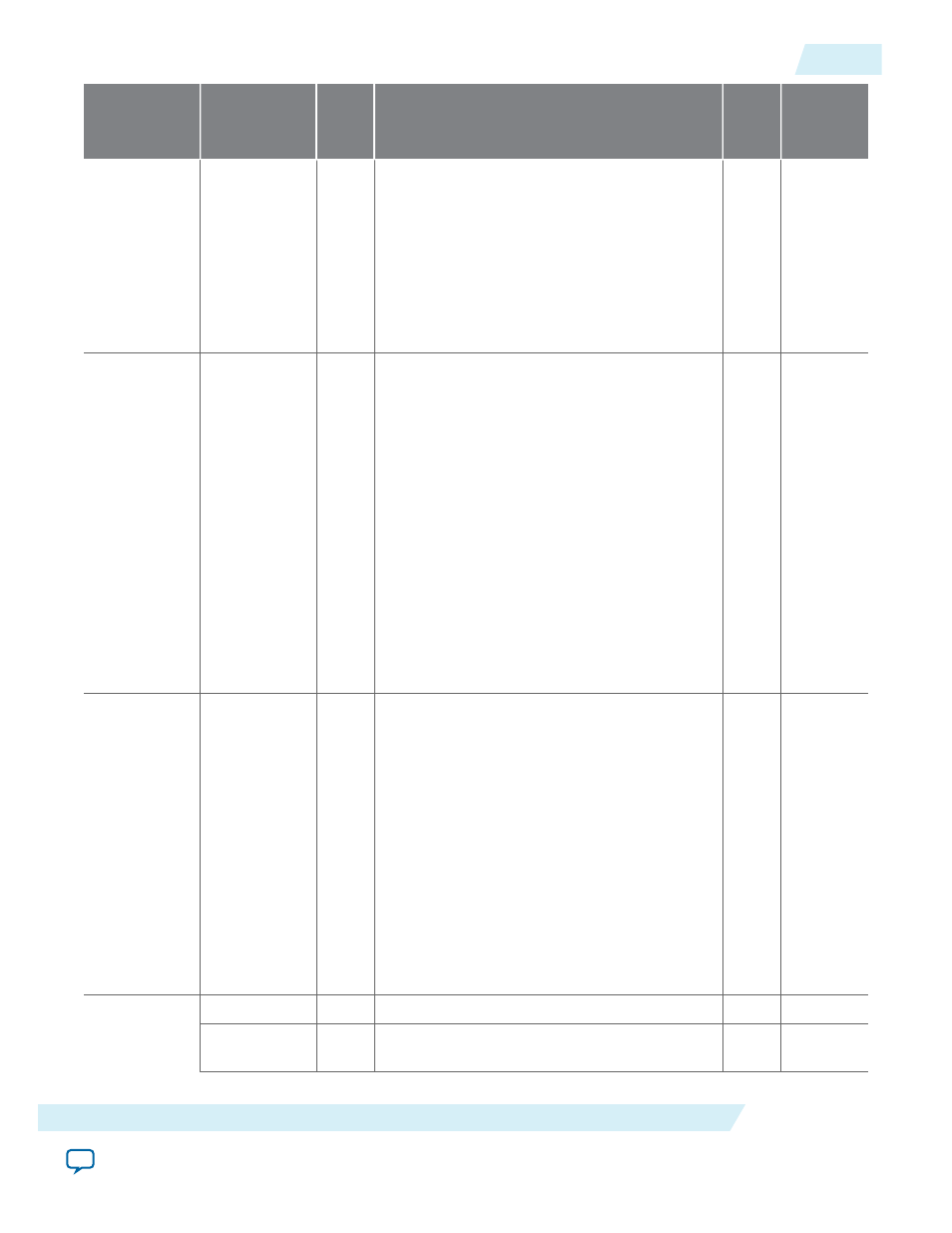

Address

Name

Bit

Description

HW

Reset

Value

Access

• 6'b000000: 1000BASE-KX

• 6'b000001: 10GBASE-KX4

• 6'b000100: 10GBASE-KR

• 6'b001000: 40GBASE-KR4

• 6'b010000: 40GBASE-CR4

• 6'b100000: 100GBASE-CR10

The only valid value for the LL 40GBASE-KR4 IP

core is 6'b001000: 40GBASE-KR4.

0x0CB

AN LP ADV

Tech_A[24:0]

[24:0] Received technology ability field bits of Clause 73

Auto Negotiation. The following protocols are

defined:

• A0 1000BASE-KX

• A1 10GBASE-KX4

• A2 10GBASE-KR

• A3 40GBASE-KR4

• A4 40GBASE-CR4

• A5 100GBASE-CR10

• A24:6 are reserved

The only valid value for the LL 40GBASE-KR4 IP

core is A3: 40GBASE-KR4..

For more information, refer to Clause 73.6.4 and

AN LP base page ability registers (7.19-7.21) of

Clause 45 of IEEE 802.3ap-2007.

25'b0 RO

0x0CC

Override AN

Channel

Select

[3:0]

If you set the value of the Override AN Channel

Enable register field (0xC0[6]) to the value of 1,

then while 0xC0[6] has the value of 1, the value

in this register field (0xCC[3:0])overrides the

master channel you set with the Auto-Negotia‐

tion Master parameter.

This register field has the following valid values:

• 4'b0001: Selects Lane 0

• 4'b0010: Selects Lane 1

• 4'b0100: Selects Lane 2

• 4'b1000: Selects Lane 3

All other values are invalid. The new master

channel is encoded with one-hot encoding.

4'b0

RW

0x0D0

Reserved

[3:2]

Reserved

Reserved

[14:12

]

Reserved

UG-01172

2015.05.04

LL 40GBASE-KR4 Registers

3-75

Functional Description

Altera Corporation