Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 52

Low Latency 40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

The Low Latency 40-100GbE IP core TX datapath with adapters employs the Avalon-ST protocol. The

Avalon-ST protocol is a synchronous point-to-point, unidirectional interface that connects the producer

of a data stream (source) to a consumer of data (sink). The key properties of this interface include:

• Start of packet (SOP) and end of packet (EOP) signals delimit frame transfers.

• A valid signal qualifies signals from source to sink.

• The sink applies backpressure to the source by using the ready signal. The source typically responds to

the deassertion of the ready signal from the sink by driving the same data until the sink can accept it.

The

readyLatency

defines the relationship between assertion and deassertion of the ready signal, and

cycles which are considered to be

ready

for data transfer.The

readyLatency

on the TX client interface

is zero cycles.

Altera provides an Avalon-ST interface with adapters for both the LL 40GbE and LL 100GbE IP cores.

The Avalon-ST interface requires that the start of packet (SOP) always be in the MSB, simplifying the

interpretation and processing of incoming data.

In the LL 40GbE IP core, the interface width is 256 bits, and in the LL 100GbE IP core, the interface width

is 512 bits. The LL 40GbE Avalon-ST interface operates at 312.5 MHz and the LL 100GbE Avalon-ST

interface operates at 390.625 MHz.

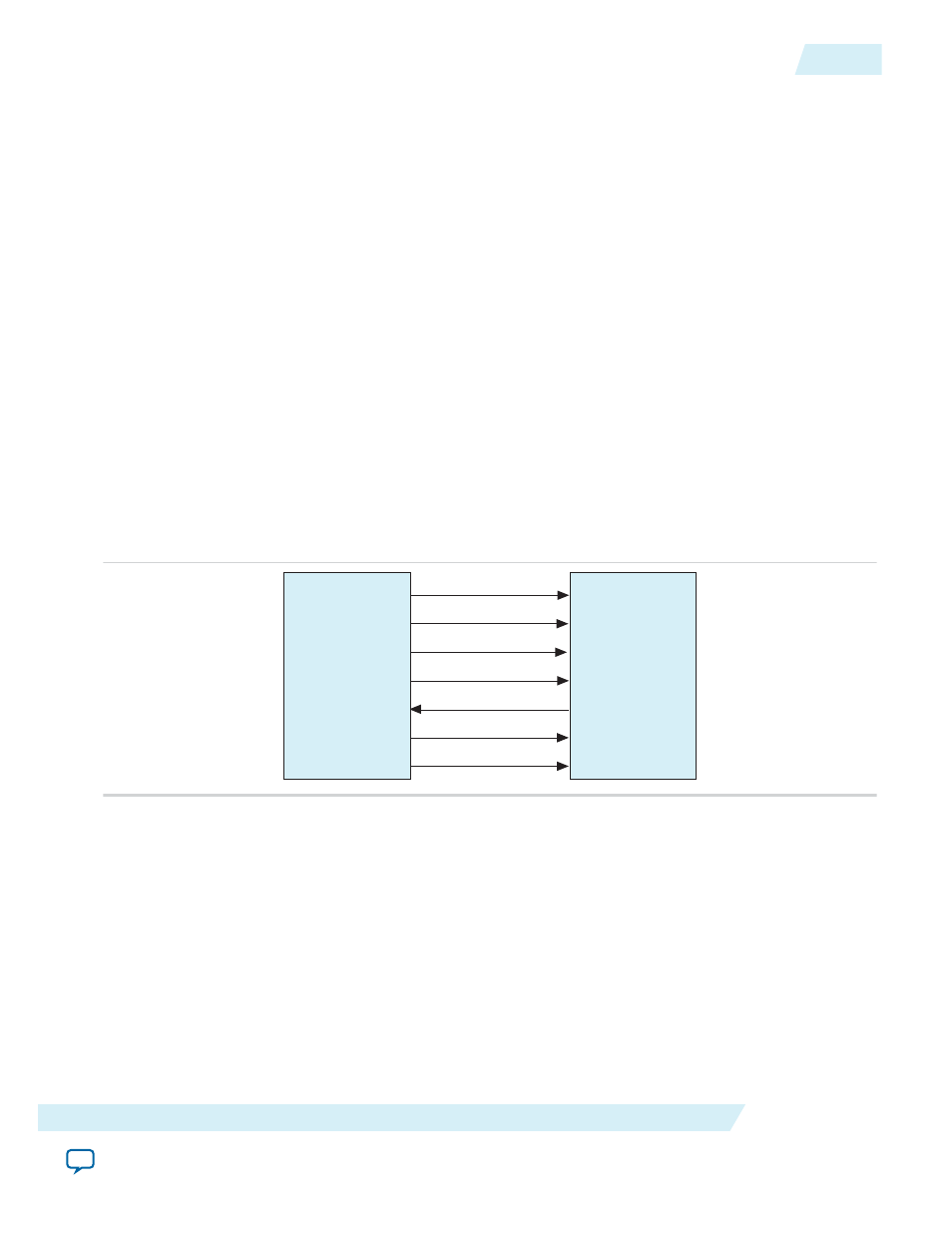

The client acts as a source and the TX MAC acts as a sink in the transmit direction.

Figure 3-3: TX Client to MAC Interface with Adapters (Avalon-ST)

The Avalon-ST interface bus width varies with the IP core variation. In the figure,

IP core and

2

(8*

l

l

l

l

l

l

l

TX MAC

TX Client

Logic

UG-01172

2015.05.04

Low Latency 40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

3-7

Functional Description

Altera Corporation