Pause control frame filtering, Pause control frame filtering -31 – Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 76

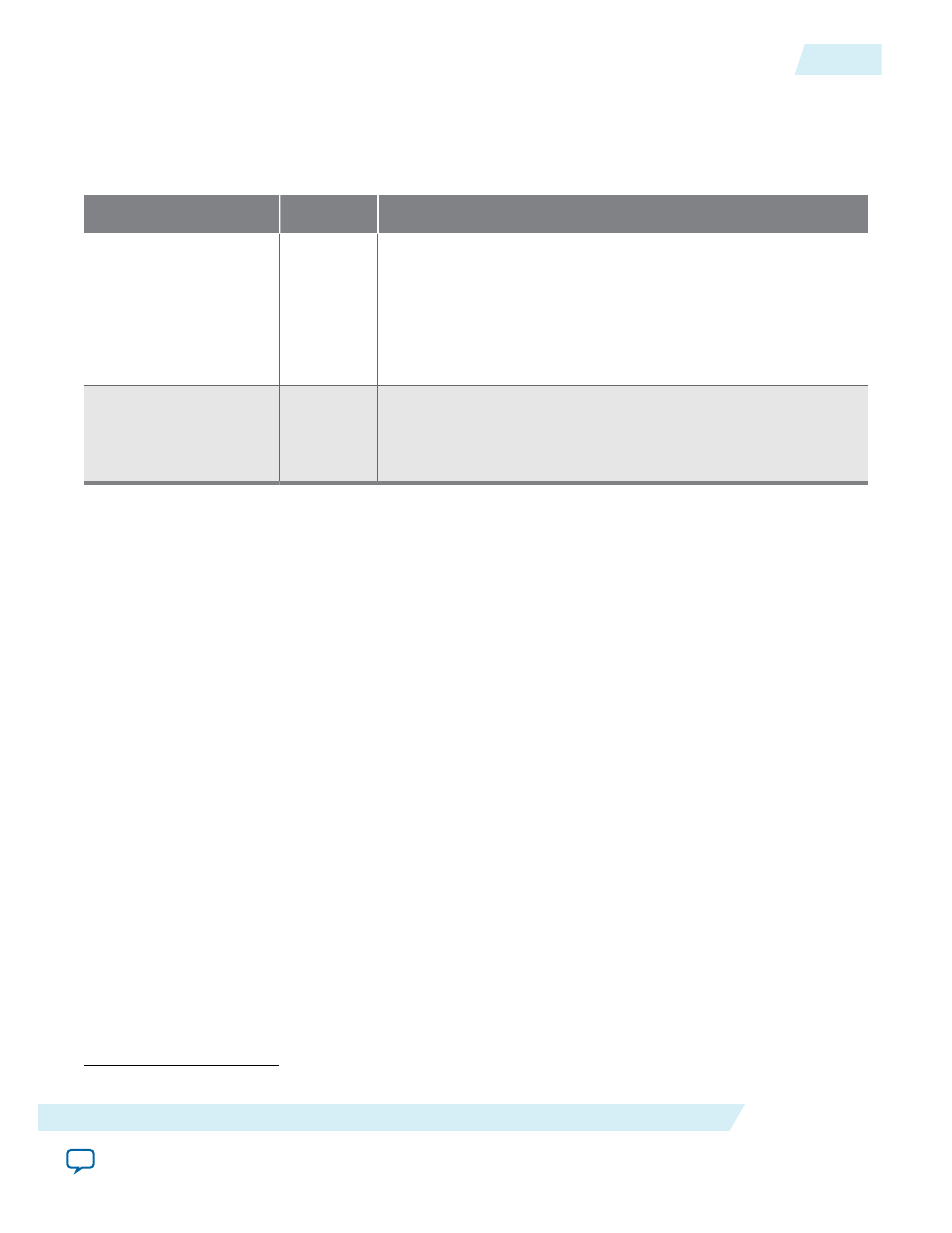

Table 3-7: Pause Control and Generation Signals

Describes the signals that implement pause control. These signals are available only if you turn on flow control in

the LL 40-100GbE parameter editor or you upgrade your IP core from an earlier release in which the signals are

available in any case.

Signal Name

Direction

Description

pause_insert_tx[N-

1:0]

(8)

Input

Level signal which directs the IP core to insert a pause frame for

priority traffic class [n] on the Ethernet link. If bit [n] of the

TX_

PAUSE_EN

register has the value of 1, the IP core transmits an

XOFF frame when this signal is first asserted. If you enable

retransmission, the IP core continues to transmit XOFF frames

periodically until the signal is de-asserted. When the signal is

deasserted, the IP core inserts an XON frame.

pause_receive_rx[N-

1:0]

(8)

Output

Asserted to indicate an RX pause signal match. The IP core asserts

bit [n] of this signal when it receives a pause request with an

address match, to signal the TX MAC to throttle its transmissions

from priority queue [n] on the Ethernet link.

Related Information

•

on page 3-31

Information about enabling and disabling the pause packets pass-through.

•

You can access the pause functionality using the pause registers for any 40-100GbE IP core variation

that includes a MAC component. Values you program in the registers specify the pause quanta.

Pause Control Frame Filtering

The Low Latency 40GbE and 100GbE IP cores support options to enable or disable the following features

for incoming pause control frames. These options are available if you set the Flow control mode

parameter to the value of Standard flow control or Priority-based flow control.

(8)

N is the number of priority queues. If the IP core implements Ethernet standard flow control, N is 1.

UG-01172

2015.05.04

Pause Control Frame Filtering

3-31

Functional Description

Altera Corporation