Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 68

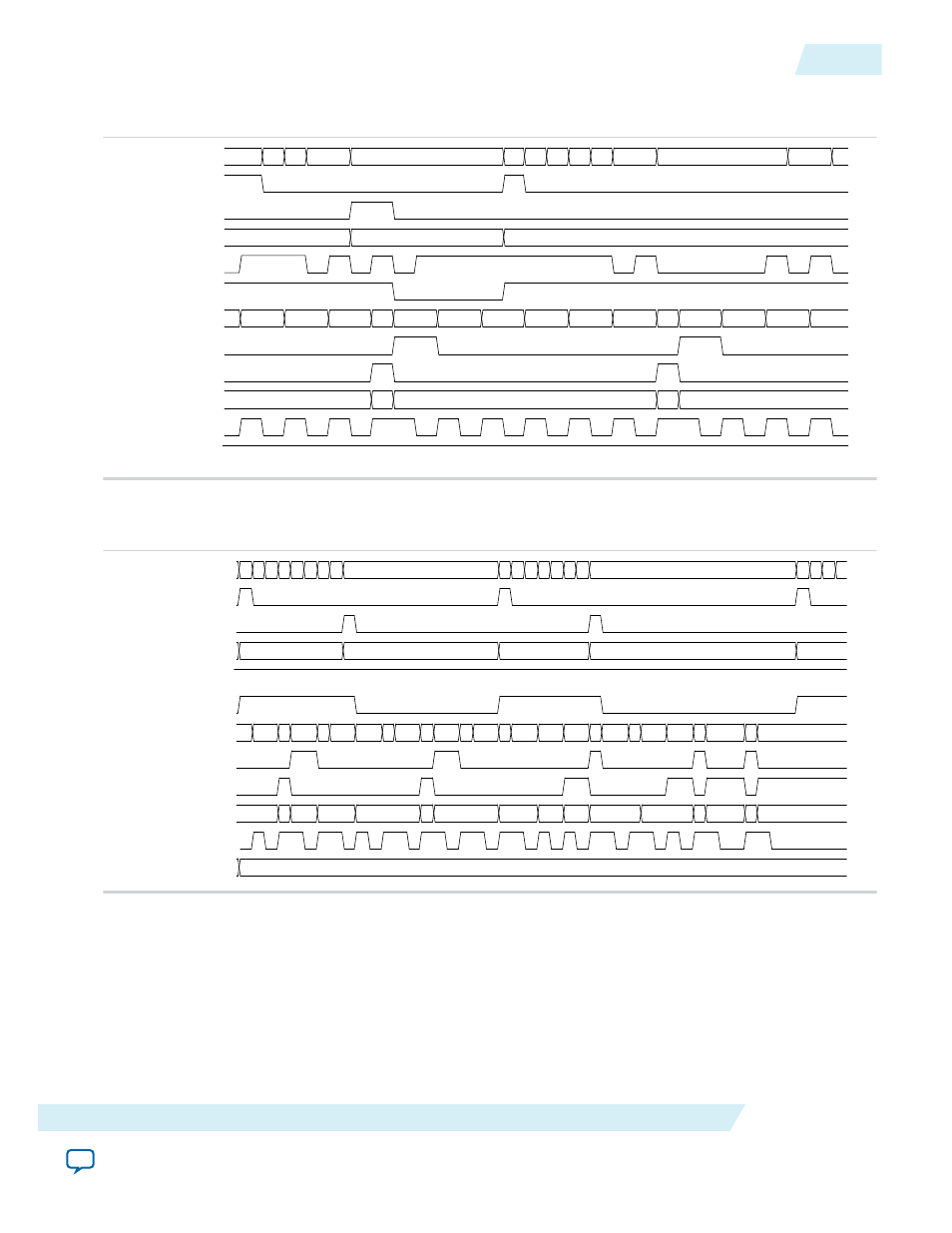

Figure 3-15: Traffic on the TX and RX Avalon-ST Client Interface for Low Latency 40GbE IP Core

Shows typical traffic for the TX and RX Avalon-ST interface Low Latency 40GbE IP core.

l4_tx_data[255:0]

l4_tx_startofpacket

l4_tx_endofpacket

l4_tx_empty[4:0]

l4_tx_ready

l4_tx_valid

l4_rx_data[255:0]

l4_rx_startofpacket

l4_rx_endofpacket

l4_rx_empty[4:0]

l4_rx_valid

l4_rx_error[5:0]

2 . 2 . 2 . 2C83 . 2C8300392C8300382C

. 3 . 3 . 3 . 3 . 3 . 3EF9 . 3EF900553EF90054

. 3EF9 . 3EF9

00

0D

00

.. 7B44 . 7B44 . 7B44 . E . EFB8 . EFB8 . EFB8 . EFB8 . EFB8 . EFB8 . E . EAD . EAD2 . EAD2 . EAD

.

1E

02

1A

00

Figure 3-16: Traffic on the TX and RX Avalon-ST Client Interface for Low Latency 100GbE IP Core

Shows typical traffic for the TX and RX Avalon-ST interface of the 100GbE IP core.

l8_tx_data[511:0]

l8_tx_startofpacket

l8_tx_endofpacket

l8_tx_empty[5:0]

l8_tx_ready

l8_tx_valid

l8_rx_data[511:0]

l8_rx_startofpacket

l8_rx_endofpacket

l8_rx_empty[5:0]

l8_rx_valid

l8_rx_error[5:0]

.. . . . . . . . .

7CD901437CD901427C

. . . . . . . .

3BCA01273BCA01263BCA01253

. . . . .

00

2F

00

29

00

64.. 64 . . A . . A . A . . A . . 6 . . 6 . . 6E . 6 . 07 . . FF . . FF . 07 . . FD4 . . 0707070707070

30

. 30

10

30

.

22

02

22 0D

2E

0E

. 05

.

00

Related Information

•

Low Latency 40-100GbE IP Core MAC Configuration Registers

on page 3-83

Describes the

MAX_RX_SIZE_CONFIG

and

CFG_PLEN_CHECK

registers.

•

on page 3-19

•

For more information about the Avalon-ST interface.

UG-01172

2015.05.04

Low Latency 40-100GbE IP Core RX Data Bus

3-23

Functional Description

Altera Corporation