Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 113

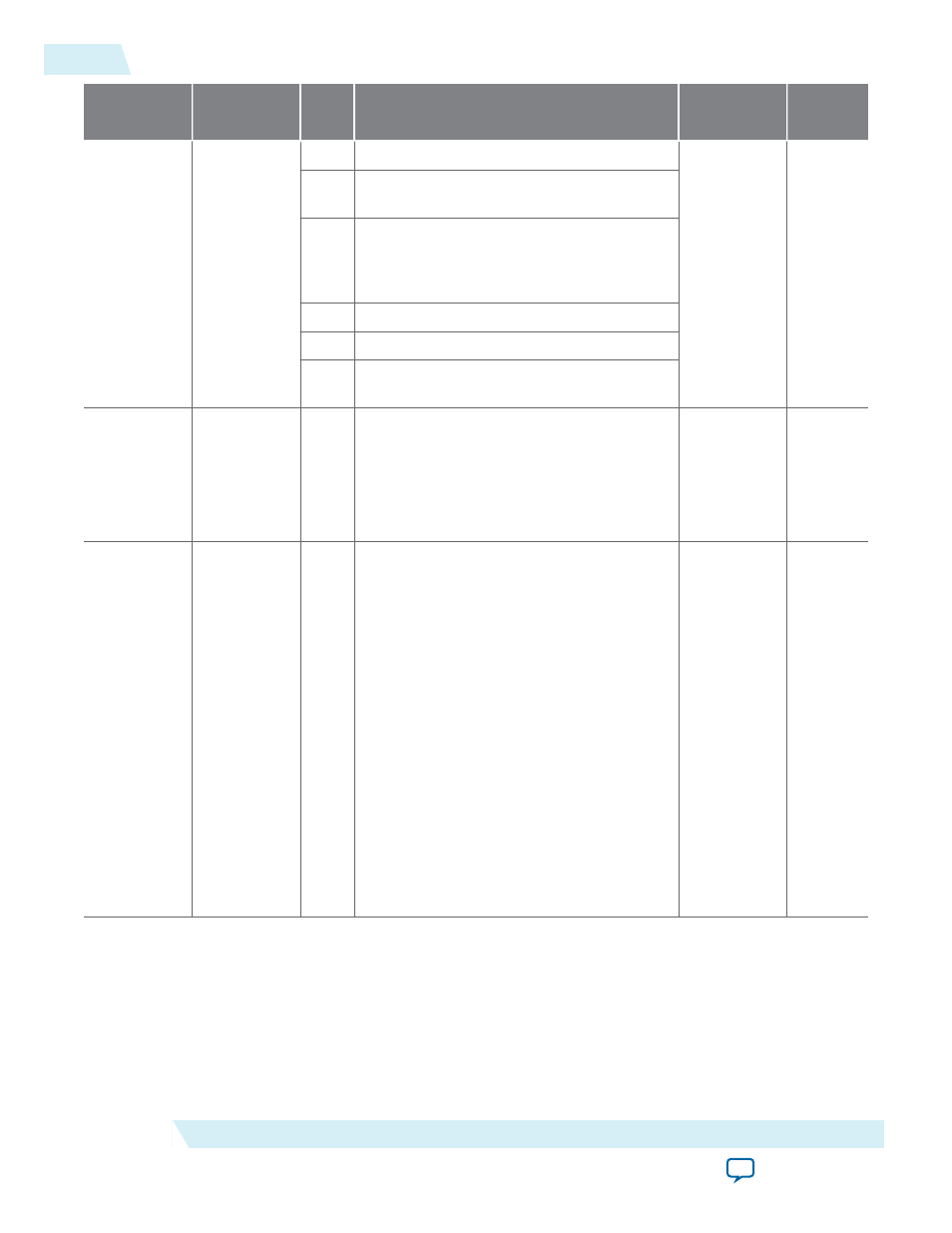

Addr

Name

Bit

Description

HW Reset

Value

Access

0x310

PHY_CONFIG

[5]

set_data_lock: Directs the PLL to lock to data.

5'b0

RW

[4]

set_ref_lock: Directs the PLL to lock to

the reference clock.

[3]

rxp_ignore_freq: Directs the IP core to

proceed with the internal reset sequence

(to reset the RX PLL) without waiting for

the RX CDR PLL to lock.

[2]

soft_rxp_rst: RX PLL soft reset

[1]

soft_txp_rst: TX PLL soft reset

[0]

eio_sys_rst: PMA system reset. Set this bit

to start the internal reset sequence.

0x313

PHY_PMA_

SLOOP

[3:0]

or

[9:0]

Serial PMA loopback. Each bit that is asserted

directs the IP core to connect the

corresponding TX–RX lane pair on the

internal loopback path, by setting the

corresponding transceiver in serial loopback

mode.

0

RW

0x314

PHY_PCS_

INDIRECT_

ADDR

[2:0] Supports indirect addressing of individual

FIFO flags in the 10G PCS Native PHY IP

core. Program this register with the encoding

for a specific FIFO flag. The flag values (one

per transceiver) are then accessible in the

PHY_PCS_INDIRECT_DATA

register.

The value in the

PHY_PCS_INDIRECT_ADDR

register directs the IP core to make available

the following FIFO flag:

• 3'b111: RX partial empty

• 3'b110: RX partial full

• 3'b101: RX empty

• 3'b100: RX full

• 3'b011: TX partial empty

• 3'b010: TX partial full

• 3'b001: TX empty

• 3'b000: TX full

8'b0

RW

3-68

PHY Registers

UG-01172

2015.05.04

Altera Corporation

Functional Description