Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 149

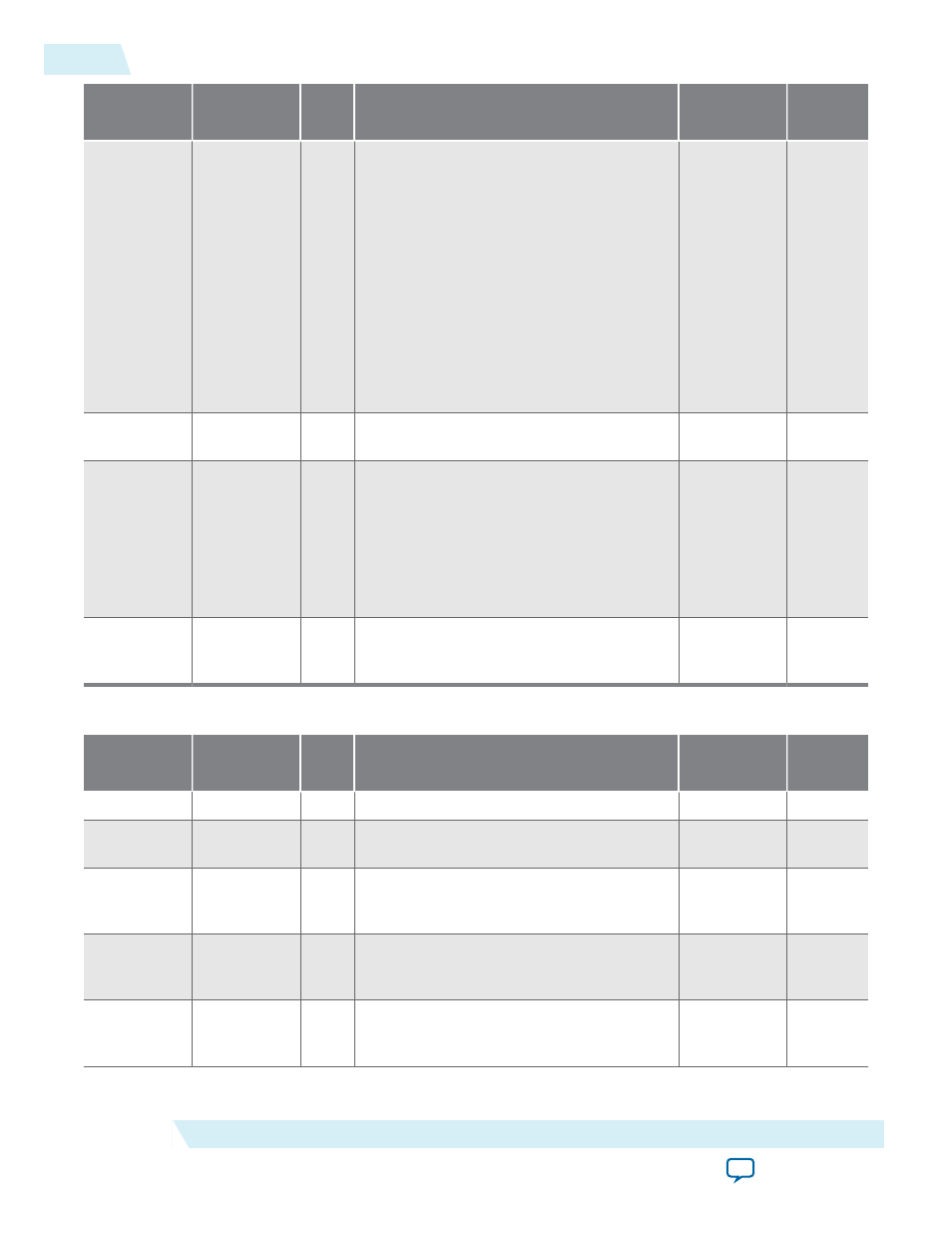

Addr

Name

Bit

Description

HW Reset

Value

Access

0xA05

TX_PTP_CLK_

PERIOD

[19:0]

clk_txmac

clock period.

Bits [19:16]: nanoseconds

Bits [15:0]: fraction of nanosecond

This value is

set to the

correct clock

period for the

required TX

MAC clock

frequency.

The clock

period is

different for

40GbE

variations and

100GbE

variations.

RW

0xA06–

0xA08

Reserved

[95:0] Reserved

96'b0

RW

0xA09

TX_PTP_

STATUS

[1:0] Bit [1]:

ptp_s2

: indicates whether the 1588

PTP module uses the two-step process (

ptp_

s2

= 1) or the one-step process (

ptp_s2

= 0).

Bit [0]:

ptp_v2

: Indicates whether the 1588

PTP module provides timestamps in

outbound Ethernet frames in V2 format

(

ptp_s2

= 1) or in V1 format (

ptp_s2

= 0).

RW

0xA0A

TX_PTP_

EXTRA_

LATENCY

[31:0] User-defined extra latency the IP core adds to

outgoing timestamps.

Table 3-31: RX 1588 PTP Registers

Addr

Name

Bit

Description

HW Reset

Value

Access

0xB00

RXPTP_REVID

[31:0] IP core revision ID.

RO

0xB01

RXPTP_

SCRATCH

[31:0] Scratch register available for testing.

32'b0

RW

0xB02

RXPTP_NAME_

0

[31:0] First 4 characters of IP core variation

identifier string "40GPTPRxCSR" or

"100GPTPRxCSR"

RO

0xB03

RXPTP_NAME_

1

[31:0] Next 4 characters of IP core variation

identifier string "40GPTPRxCSR" or

"100GPTPRxCSR"

RO

0xB04

RXPTP_NAME_

2

[31:0] Final 4 characters of IP core variation

identifier string "40GPTPRxCSR" or

"100GPTPRxCSR"

RO

3-104

1588 PTP Registers

UG-01172

2015.05.04

Altera Corporation

Functional Description