Bus quantization effects with adapters – Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 56

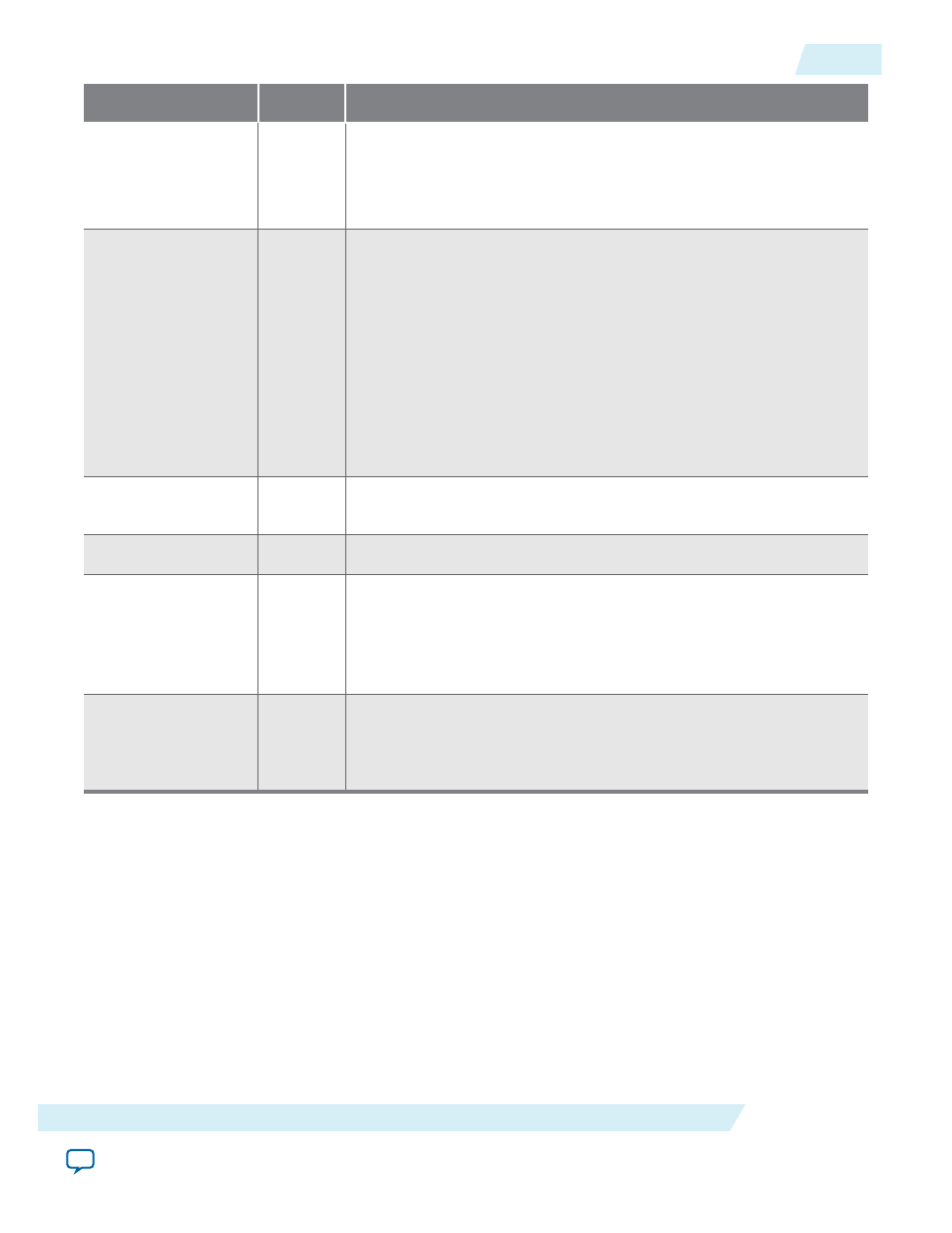

Signal Name

Direction

Description

din_eop[

Input

End of packet location in the TX data bus. Indicates the 64-bit word

that holds the end-of-packet byte. Any byte may be the last byte in a

packet.

Bit 0 of

din_eop

corresponds to the data word in

din[63:0]

.

din_eop_

empty[

Input

Indicates the number of empty (invalid) bytes in the end-of-packet

byte in the word indicated by

din_eop

.

If

din_eop[z]

has the value of 0, then the value of

din_eop_empty[(z

+2):z]

does not matter. However, if

din_eop[z]

has the value of 1,

then you must set the value of

din_eop_empty[(z+2):z]

to the

number of empty (invalid) bytes in the end-of-packet word

z

.

For example, if you have a 100GbE IP core and want to indicate that in

the current

clk_txmac

clock cycle, byte 6 in word 2 of

din

is an end-

of-packet byte, and no other words hold an end-of-packet byte in the

current clock cycle, you must set the value of

din_eop

to 4'b0100 and

the value of

din_eop_empty

to 12'b000_110_000_000.

din_idle[

1:0]

Input

Indicates the words in

din

that hold Idle bytes or control information

rather than Ethernet data. One-hot encoded.

din_req

Output

Indicates that input data was accepted by the IP core.

tx_error[

1:0]

Input

When asserted in an EOP cycle (while

din_eop[

is non-zero)

, directs the IP core to insert an error in the corresponding packet

before sending it on the Ethernet link.

This signal is a test and debug feature. In loopback mode, the IP core

recognizes the packet upon return as a malformed packet.

clk_txmac

Output

TX MAC clock. The clock frequency should be 312.5 MHz in LL

40GbE IP cores, and 390.625 MHz in LL 100GbE IP cores. The

clk_

txmac

clock and the

clk_rxmac

clock (which clocks the RX datapath)

are assumed to have the same frequency.

The IP core reads the bytes in big endian order. A packet may start in the most significant byte of any

word. A packet may end on any byte.

Bus Quantization Effects With Adapters

The TX custom streaming interface allows a packet to start at any of two or four positions to maximize

utilization of the link bandwidth. The TX Avalon-ST interface only allows start of packet (SOP) to be

placed at the most significant position. If the SOP were restricted to the most significant position in the

client logic data bus in the custom streaming interface, bus bandwidth would be reduced.

UG-01172

2015.05.04

Bus Quantization Effects With Adapters

3-11

Functional Description

Altera Corporation