Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 108

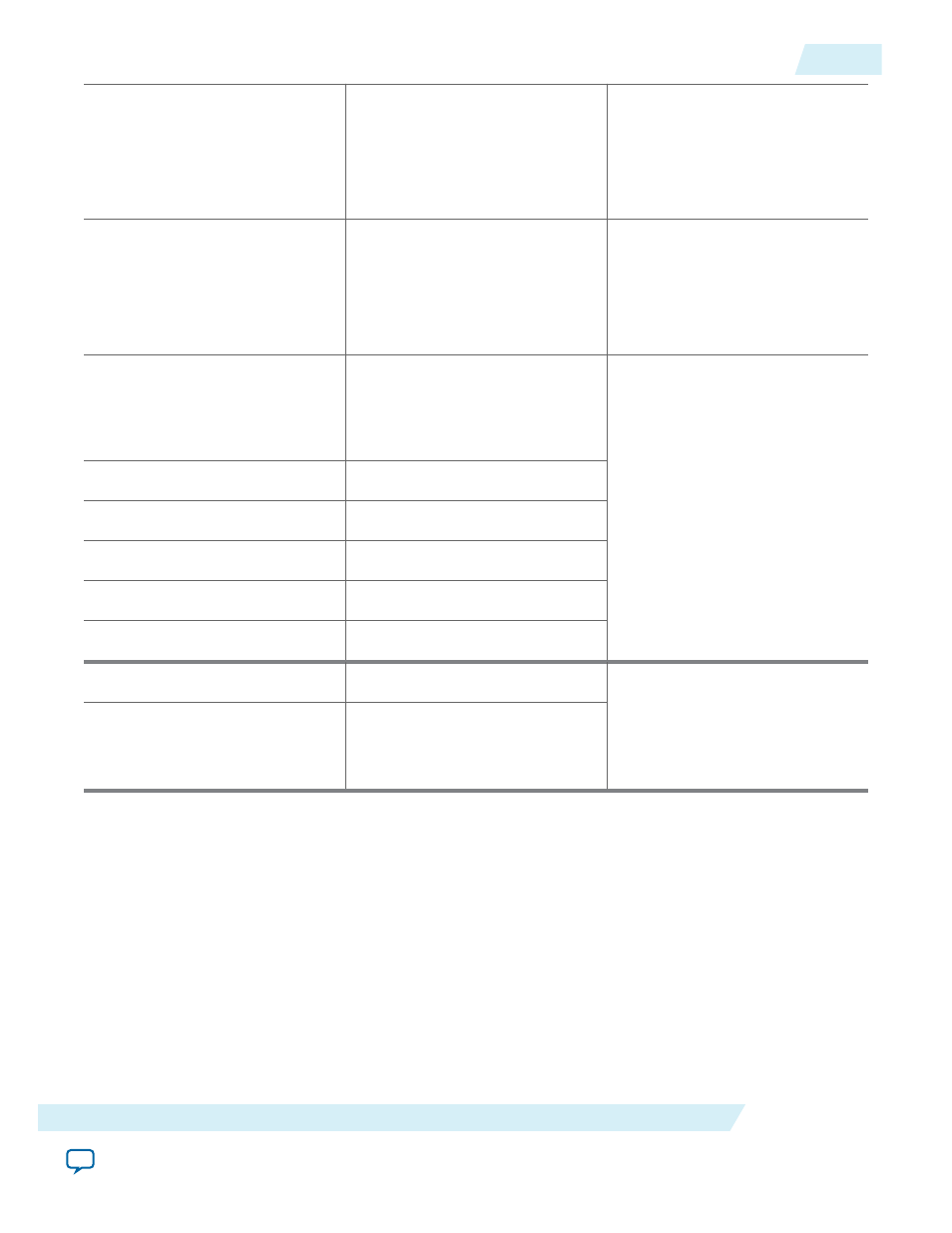

reconfig_clk

Input

Clocks

Arria 10 Native PHY IP core

reconfiguration interface

This signal is available in Arria

10 devices only.

reconfig_reset

Input

Resets

Arria 10 Native PHY IP core

reconfiguration interface

This signal is available in Arria

10 devices only.

reconfig_address

[11:0]

(40GbE and CAUI-4)

reconfig_address

[13:0]

(100GbE)

Input

Arria 10 Native PHY IP core

reconfiguration interface

These signals are available in

Arria 10 devices only.

reconfig_read

Input

reconfig_write

Input

reconfig_writedata[31:0]

Input

reconfig_readdata[31:0]

Output

reconfig_waitrequest

Output

pll_locked

Input

External transceiver PLL

interface. These signals are

available in Arria 10 devices

only.

tx_serial_clk[3:0]

(40GbE

and CAUI–4)

tx_serial_clk[9:0]

(100GbE)

Input

Related Information

•

on page 3-51

Overview of IP core clocks. Includes list of clock signals and recommended and required frequencies.

•

•

Transceiver PHY Serial Data Interface

on page 3-48

•

•

Low Latency 40-100GbE IP Core TX Data Bus with Adapters (Avalon-ST Interface)

Describes the TX client interface.

•

Low Latency 40-100GbE IP Core TX Data Bus Without Adapters (Custom Streaming Interface)

on

page 3-10

•

Low Latency 40-100GbE IP Core RX Data Bus

on page 3-20

Describes the RX client interface.

UG-01172

2015.05.04

Low Latency 40-100GbE IP Core Signals

3-63

Functional Description

Altera Corporation