Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 135

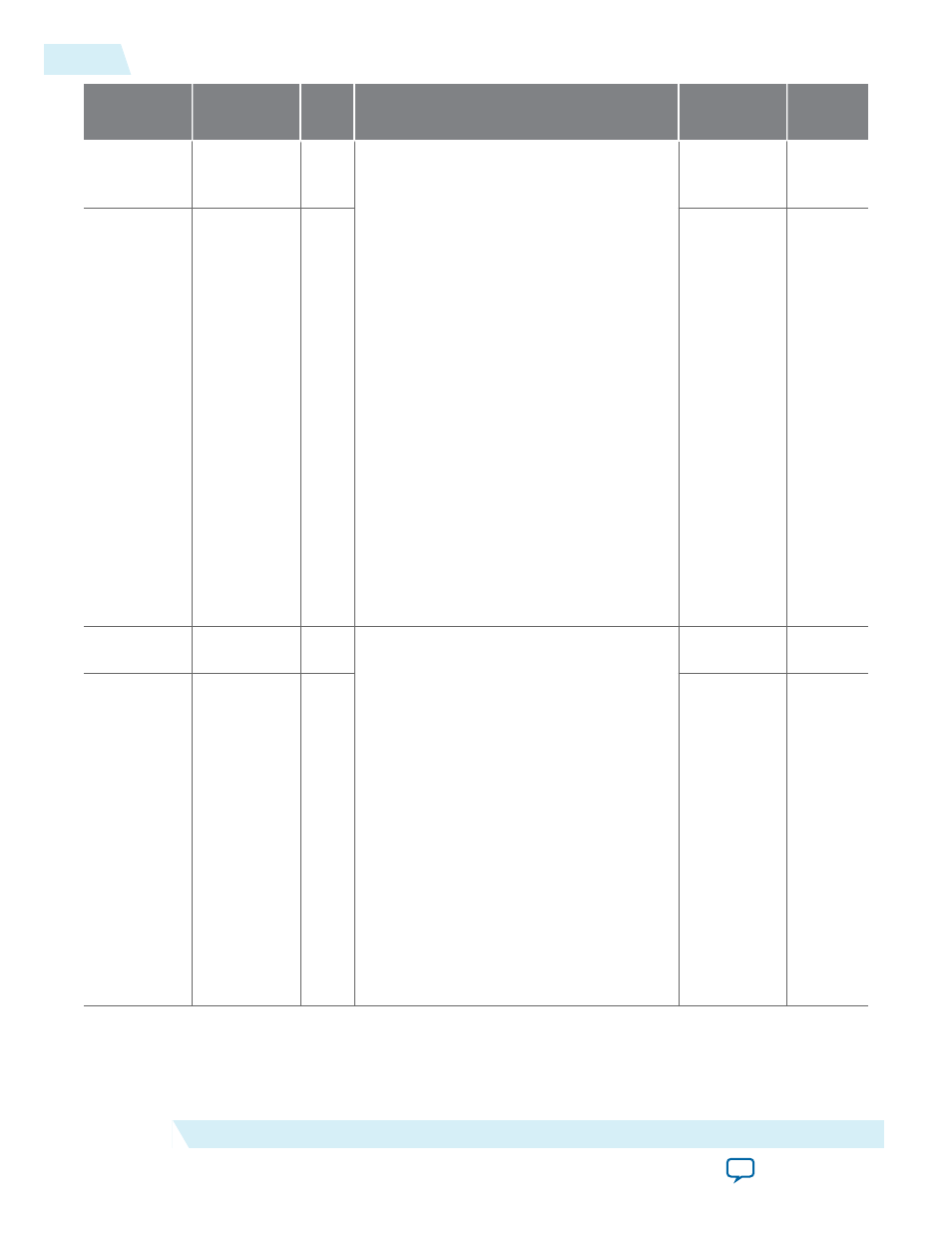

Addr

Name

Bit

Description

HW Reset

Value

Access

0x60B

CFG_

RETRANSMIT_

HOLDOFF_EN

[0]

The

CFG_RETRANSMIT_HOLDOFF_EN

and

CFG_

RETRANSMIT_HOLDOFF_QUANTA

registers

provide a mechanism to specify a uniform

retransmission hold-off delay for all priority

queues. If

CFG_RETRANSMIT_HOLDOFF_EN

has

the value of 1, the IP core enforces a

retransmission hold-off delay for each

priority queue that is the longer of the queue-

specific retransmission hold-off delay

accessible in the

RETRANSMIT_XOFF_

HOLDOFF_QUANTA

register (if enabled) and the

retransmission hold-off delay specified in the

CFG_RETRANSMIT_HOLDOFF_QUANTA

register.

CFG_RETRANSMIT_HOLDOFF_QUANTA

unit is

quanta. One quanta is 512 bit times, which

varies according to the datapath width (256

or 512 depending on the IP core variation)

and the

clk_txmac

frequency. In 100GbE IP

cores, a quanta is effectively a single

clk_

txmac

clock cycle.

These registers are present only if you set the

value of Flow control mode to Priority-

based flow control in the LL 40-100GbE

parameter editor.

1'b0

RW

0x60C

CFG_

RETRANSMIT_

HOLDOFF_

QUANTA

[15:0]

0x60D

TX_PFC_

DADDRL

[31:0]

TX_PFC_DADDRH

contains the 16 most signifi‐

cant bits of the destination address for PFC

pause frames.

TX_PFC_DADDRL

contains the 32 least signifi‐

cant bits of the destination address for PFC

pause frames.

This feature allows you to program a destina‐

tion address other than the standard

multicast address for PFC frames, for debug

or proprietary purposes.

{TX_PFC_DADDRH[15:0],TX_PFC_

DADDRL[31:0]}

can be a broadcast,

muilticast, or unicast address.

These registers are present only if you set the

value of Flow control mode to Priority-

based flow control in the LL 40-100GbE

parameter editor.

0xC200_0001 RW

0x60E

TX_PFC_

DADDRH

[15:0]

0x0180

RW

3-90

Pause Registers

UG-01172

2015.05.04

Altera Corporation

Functional Description