1588 ptp registers – Altera Low Latency 40-Gbps Ethernet MAC and PHY MegaCore Function User Manual

Page 148

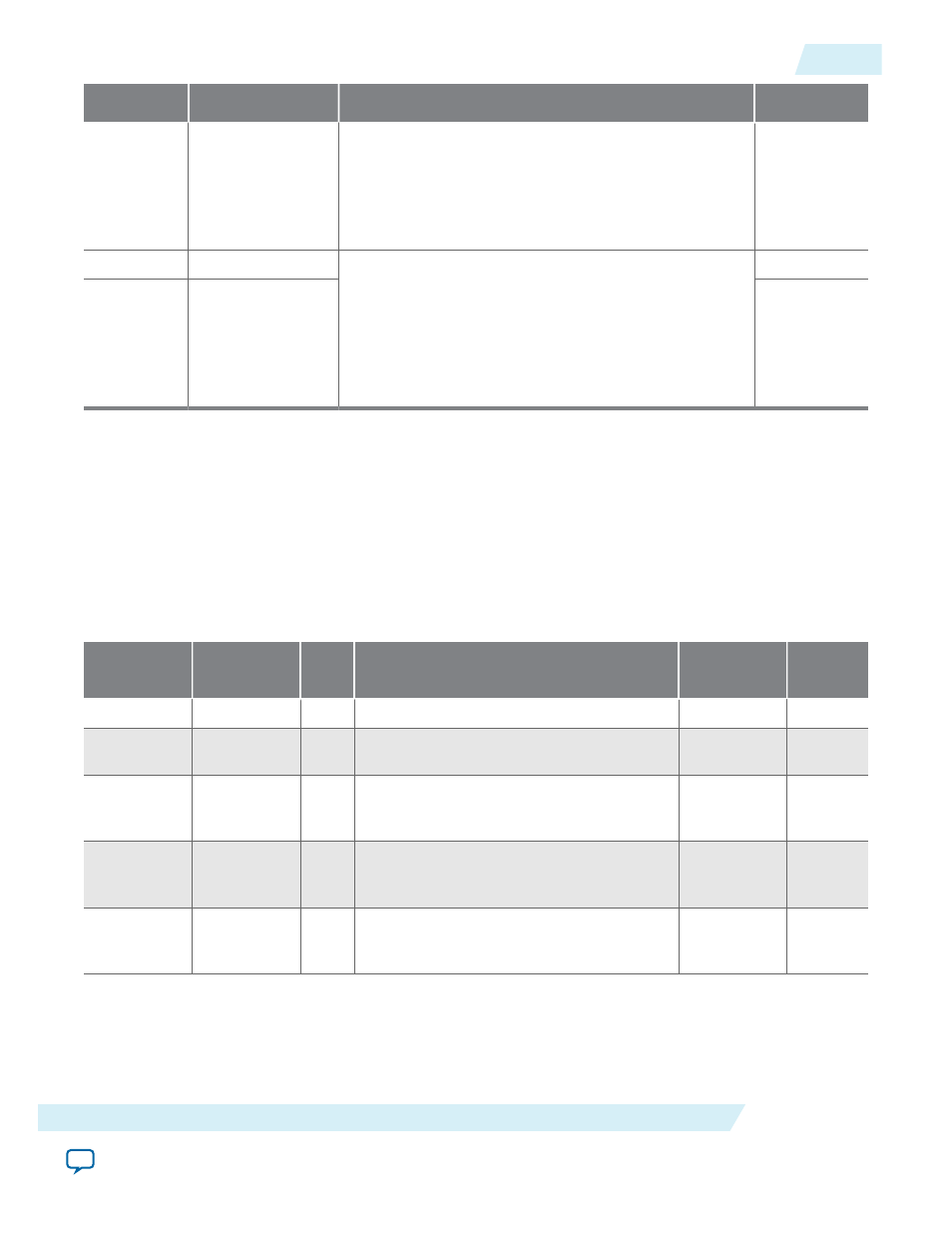

Address

Name-

Description

Access

0x946

CNTR_RX_STATUS

• Bit [1]: Indicates that the RX statistics registers are

paused (while

CNTR_RX_CONFIG[2]

is asserted) .

• Bit [0]: Indicates the presence of at least one parity

error in the RX statistics counters.

Bits [31:2] are Reserved.

RO

0x960

RxOctetsOK_LO

Number of received payload bytes in frames with no FCS,

undersized, oversized, or payload length errors. This

register is compliant with section 5.2.1.14 of the IEEE

Standard 802.3-2008.

Instead of an increment vector, this register corresponds to

the signals

rx_inc_octetsOK[15:0]

and

rx_inc_

octetsOK_valid

.

RO

0x961

RxOctetsOK_HI

RO

Related Information

1588 PTP Registers

The 1588 PTP registers together with the 1588 PTP signals process and provide Precision Time Protocol

(PTP) timestamp information as defined in the IEEE 1588-2008 Precision Clock Synchronization Protocol

for Networked Measurement and Control Systems Standard. The 1588 PTP module provides you the

support to implement the 1588 Precision Time Protocol in your design.

Table 3-30: TX 1588 PTP Registers

Addr

Name

Bit

Description

HW Reset

Value

Access

0xA00

TXPTP_REVID

[31:0] IP core revision ID.

RO

0xA01

TXPTP_

SCRATCH

[31:0] Scratch register available for testing.

32'b0

RW

0xA02

TXPTP_NAME_

0

[31:0] First 4 characters of IP core variation

identifier string "40gPTPTxCSR" or

"100gPTPTxCSR"

RO

0xA03

TXPTP_NAME_

1

[31:0] Next 4 characters of IP core variation

identifier string "40gPTPTxCSR" or

"100gPTPTxCSR"

RO

0xA04

TXPTP_NAME_

2

[31:0] Final 4 characters of IP core variation

identifier string "40gPTPTxCSR" or

"100gPTPTxCSR"

RO

UG-01172

2015.05.04

1588 PTP Registers

3-103

Functional Description

Altera Corporation