Altera IP Compiler for PCI Express User Manual

Page 94

5–8

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

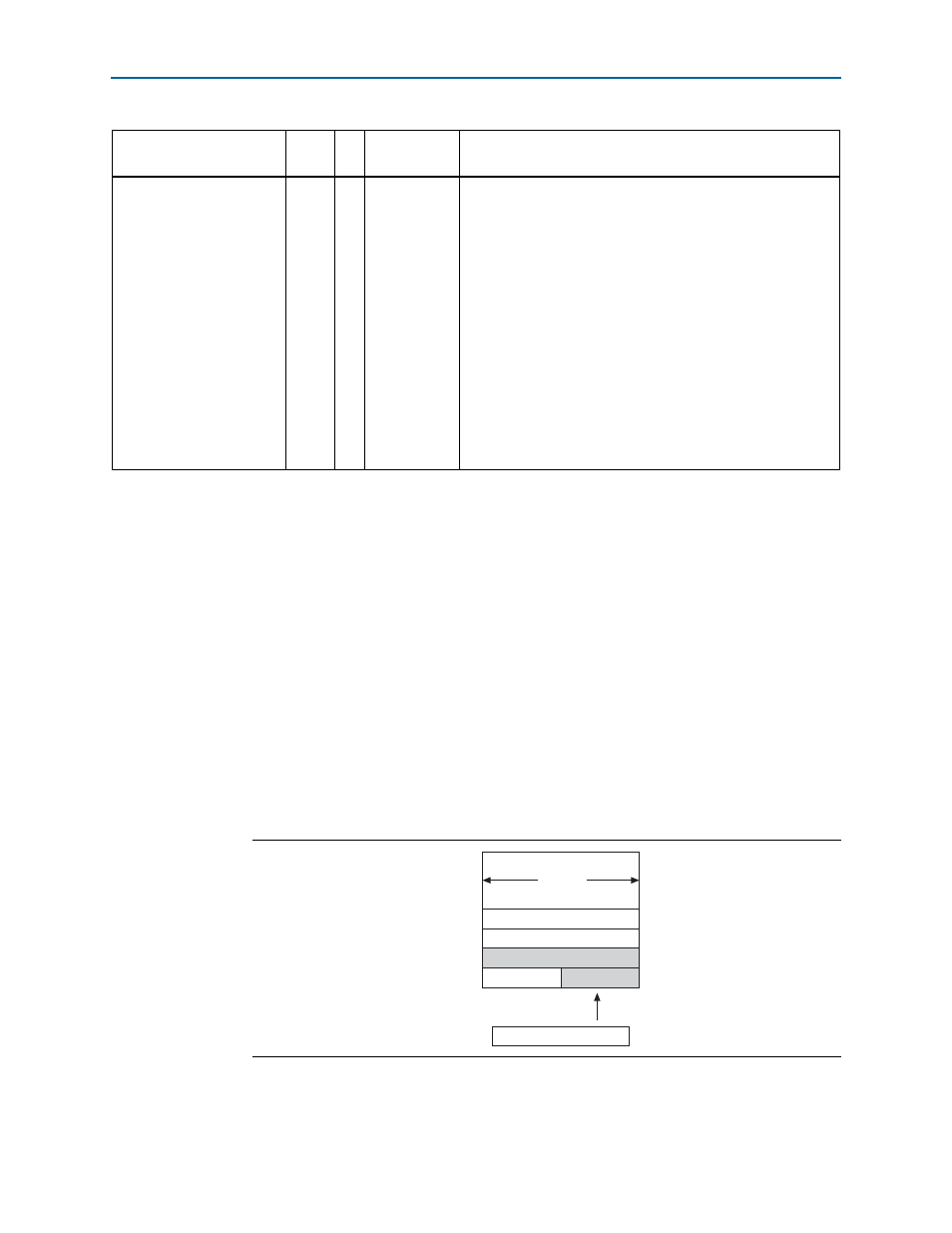

To facilitate the interface to 64-bit memories, the IP core always aligns data to the

qword or 64 bits; consequently, if the header presents an address that is not qword

aligned, the IP core, shifts the data within the qword to achieve the correct alignment.

shows how an address that is not qword aligned, 0x4, is stored in memory.

The byte enables only qualify data that is being written. This means that the byte

enables are undefined for 0x0–0x3. This example corresponds to

. Qword alignment is a feature of the IP core that cannot be turned off.

Qword alignment applies to all types of request TLPs with data, including memory

writes, configuration writes, and I/O writes. The alignment of the request TLP

depends on bit 2 of the request address. For completion TLPs with data, alignment

depends on bit 2 of the lower address field. This bit is always 0 (aligned to qword

boundary) for completion with data TLPs that are for configuration read or I/O read

requests.

f

Appendix A, Transaction Layer Packet (TLP) Header Formats

of all TLPs.

rx_st_be

8, 16

O

component

specific

These are the byte enables corresponding to the transaction

layer's rx_be. The byte enable signals only apply to PCI

Express TLP payload fields. When using a 64-bit Avalon-ST

bus, the width of rx_st_be is 8. When using a 128-bit Avalon-

ST bus, the width of rx_st_be is 16. This signal is optional.

You can derive the same information decoding the FBE and LBE

fields in the TLP header. The correspondence between byte

enables and data is as follows when the data is aligned:

rx_st_data[63:56]

= rx_st_be[7]

rx_st_data[55:48]

= rx_st_be[6]

rx_st_data[47:40]

= rx_st_be[5]

rx_st_data[39:32]

= rx_st_be[4]

rx_st_data[31:24]

= rx_st_be[3]

rx_st_data[23:16]

= rx_st_be[2]

rx_st_data[15:8]

= rx_st_be[1]

rx_st_data[7:0]

= rx_st_be[0]

Notes to

(1) In Stratix IV GX devices,

(2) The RX interface supports a readyLatency of 2 cycles for the hard IP implementation and 3 cycles for the soft IP implementation.

Table 5–2. 64- or 128-Bit Avalon-ST RX Datapath (Part 3 of 3)

Signal

Width

Dir

Avalon-ST

Type

Description

Figure 5–4. Qword Alignment

.

.

.

0x0

0x8

0x10

0x18

Header

Addr = 0x4

64 bits

PCB Memory

Valid Data

Valid Data