Altera IP Compiler for PCI Express User Manual

Page 140

5–54

Chapter 5: IP Core Interfaces

Physical Layer Interface Signals

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

An offset_cancellation_reset input signal keeps the altgxb_reconfig block in

reset until the reconfig_clk and fixedclk_serdes clock are stable. This signal is not

currently visible at the interface by default. Refer to

and its

explanation.

The input signals listed in

connect from the user application directly to the

transceiver instance.

f

For more information refe

e

in volume 3 of the

Stratix IV Device

Handbook

, or

, as

appropriate.

The following sections describe signals for the three possible types of physical

interfaces (1-bit, 20-bit, or PIPE). Refer to

,

for pinout diagrams

of all of the IP Compiler for PCI Express variations.

busy_altgxb_reconfig

I

When asserted, indicates that offset calibration is calibrating the transceiver. This

signal is used in the hard IP implementation for Arria II GX, Arria II GZ,

Cyclone IV GX, HardCopy IV GX, and Stratix IV GX devices.

Note to

:

(1) Two signal names are listed only when the Qsys signal names differ.

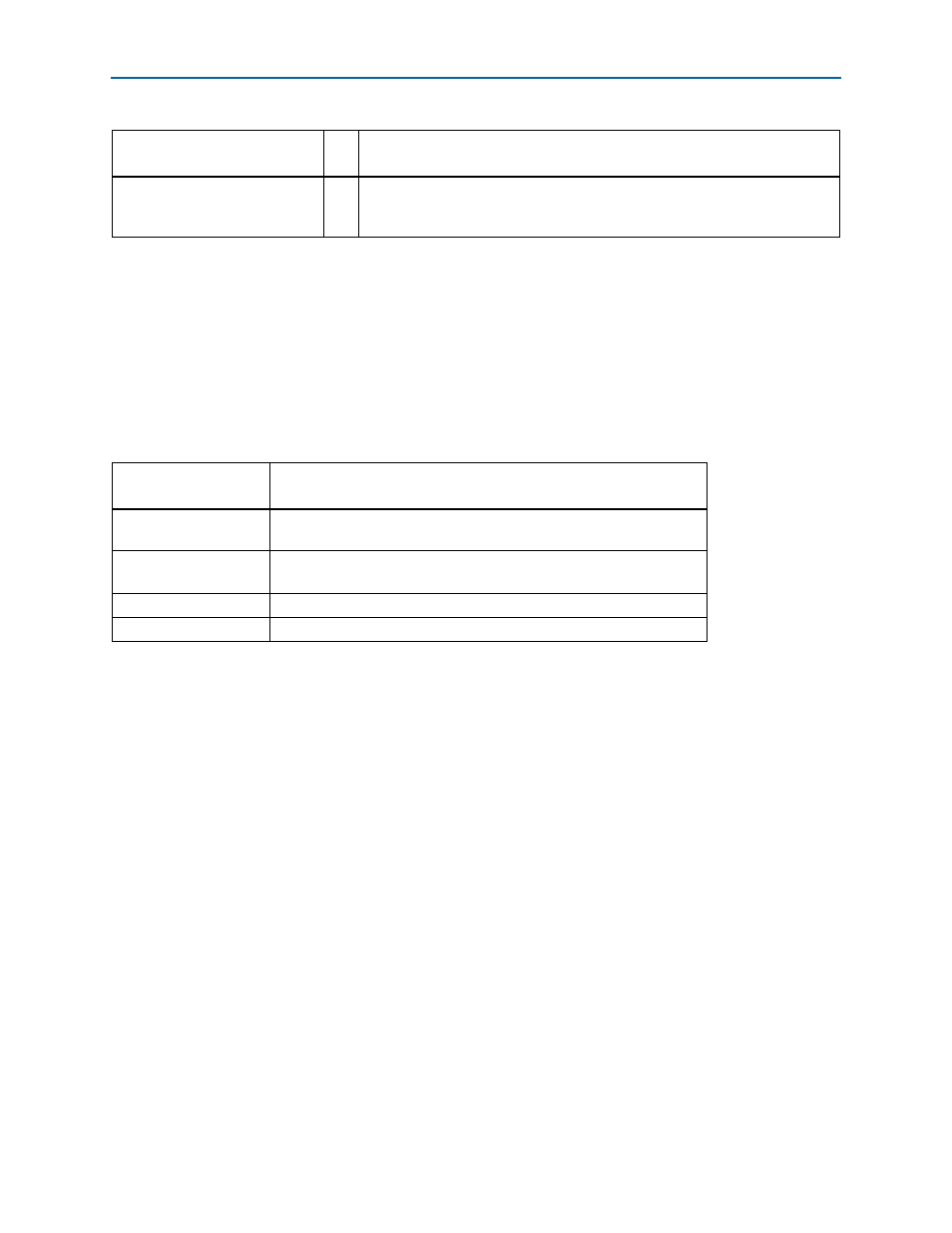

Table 5–28. Transceiver Control Signals (Part 2 of 2)

Signal Name in

Qsys

(1)

I/O

Description

Table 5–29. Transceiver Control Signal Use

Signal Name in

Qsys

Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX Devices

cal_blk_clk/

cal_blk_clk_clk

Yes

reconfig_clk/

reconfig_gxbclk_clk

Yes

reconfig_togxb

Yes

reconfig_fromgxb

Yes

Note to

:

(1) Two signal names are listed only when the Qsys signal names differ.