Figure 5–3 – Altera IP Compiler for PCI Express User Manual

Page 90

5–4

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

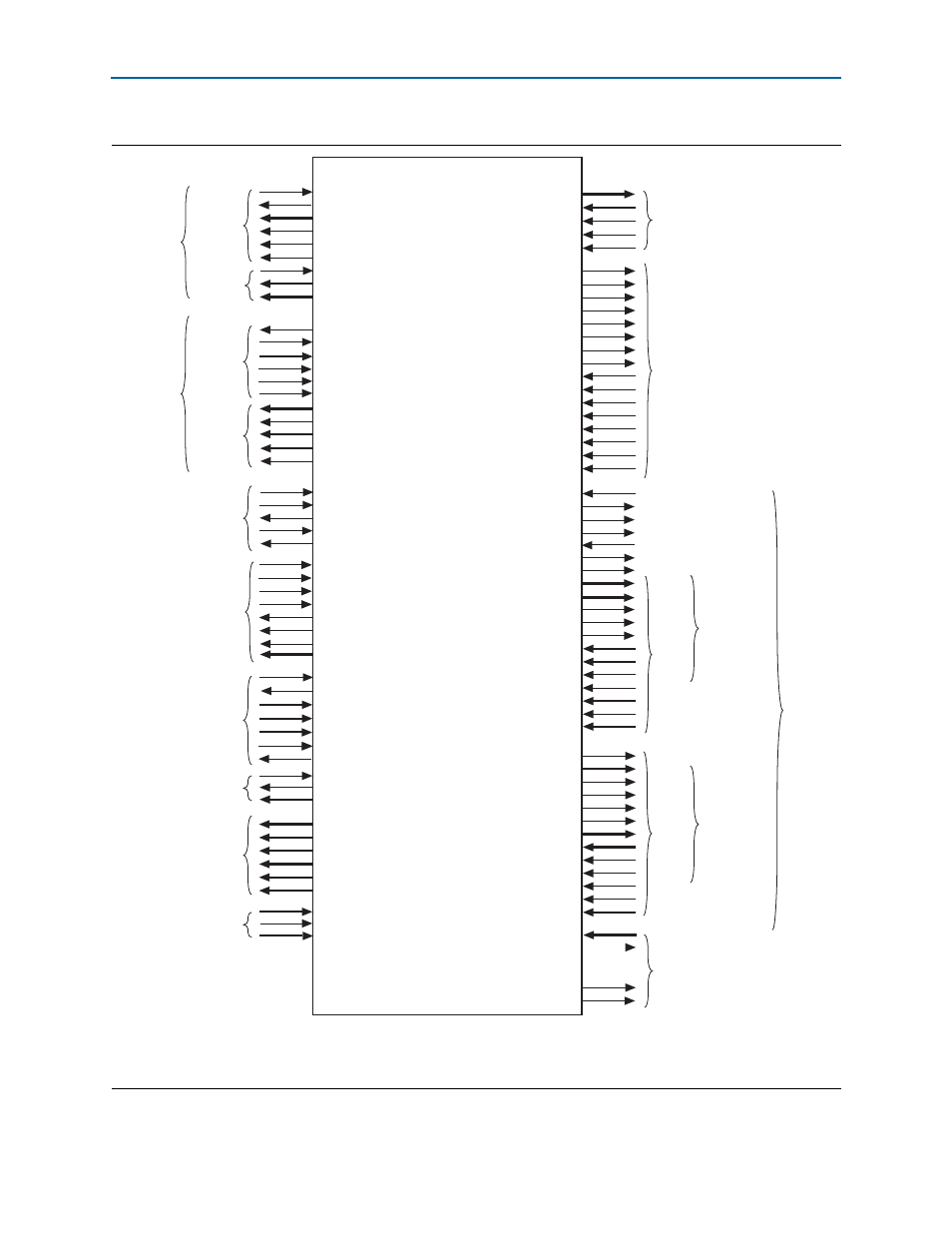

Figure 5–3. Signals in the Soft IP Implementation with Avalon-ST Interface

Notes to

(1) Available in Stratix IV GX devices. For Stratix IV GX devices,

(2) Available in Stratix IV GX devices. For Stratix IV GX reconfig_togxb,

rx_st_ready0

rx_st_valid0

rx_st_data0[63:0]

rx_st_sop0

rx_st_eop0

rx_st_err0

rx_st_mask0

rx_st_bardec0[7:0]

rx_st_be0[7:0]

tx_st_ready0

tx_st_valid0

tx_st_data0[63:0]

tx_st_sop0

tx_st_eop0

tx_st_err0

tx_cred0[35..0]

tx_fifo_empty0

tx_fifo_rdptr0[3:0]

tx_fifo_wrptr0[3:0]

tx_fifo_full0

refclk

clk250_in - x8

clk250_out - x8

clk125_in - x1 and x4

clk125_out - x1 and x4

npor

srst - x1 and x4

crst - x1 and x4

rstn - x8

l2_exit

hotrst_exit

dlup_exit

dl_ltssm[4:0]

app_msi_req

app_msi_ack

app_msi_tc [2:0]

app_msi_num [4:0]

pex_msi_num [4:0]

app_int_sts

app_int_ack - x1 and x4

pme_to_cr

pme_to_sr

cfg_pmcsr[31:0]

cfg_tcvcmap [23:0]

cfg_busdev [12:0]

cfg_prmcsr [31:0]

cfg_devcsr [31:0]

cfg_linkcsr [31:0]

cfg_msicsr [15:0]

cpl_err[6:0]

cpl_pending

err_desc_func0 [127:0]- x1, x4

pipe_mode

pipe_rstn

pipe_txclk

rate_ext

xphy_pll_areset

xphy_pll_locked

txdetectrx_ext

txdata0_ext[15:0]

txdatak0_ext[1:0]

txelecidle0_ext

txcompl0_ext

rxpolarity0_ext

rxdata0_ext[15:0]

rxdatak0_ext[1:0]

rxvalid0_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

phystatus_ext

powerdown_ext[1:0]

txdetectrx_ext

txdata0_ext[7:0]

txdatak0_ext

txelecidle0_ext

txcompl0_ext

rxpolarity0_ext

powerdown_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

test_in[31:0]

test_out[511:0]

tx_st_fifo_empty0

tx_st_fifo_full0

IP Compiler for PCI Express Soft IP Implementation

Interrupt

Clock

Reset

Test

Interface

Tx Port

(Path to

Virtual

Channel 0)

Power

Mnmt

Config

Completion

Interface

Rx Port

(Path to

Virtual

Channel 0)

reconfig_fromgxb[

:0]

reconfig_togxb[

:0]

reconfig_clk

cal_blk_clk

gxb_powerdown

Transceiver

Control

8-bit

PIPE

for x8

16-bit

PIPE

for x1

and x4

for

external

PHY

for

internal

PHY

Repeated for

Lanes 1-7 in

x8 MegaCore

Repeated for

Lanes 1-3 in

x4 MegaCore

tx_out0

tx_out1

tx_out2

tx_out3

tx_out4

tx_out5

tx_out6

tx_out7

rx_in0

rx_in1

rx_in2

rx_in3

rx_in4

rx_in5

rx_in6

rx_in7

Serial

IF to

PIPE

( user specified,

up to 512 bits)

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

×1 and ×4 only

(1)

(2)