Altera IP Compiler for PCI Express User Manual

Page 46

3–10

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

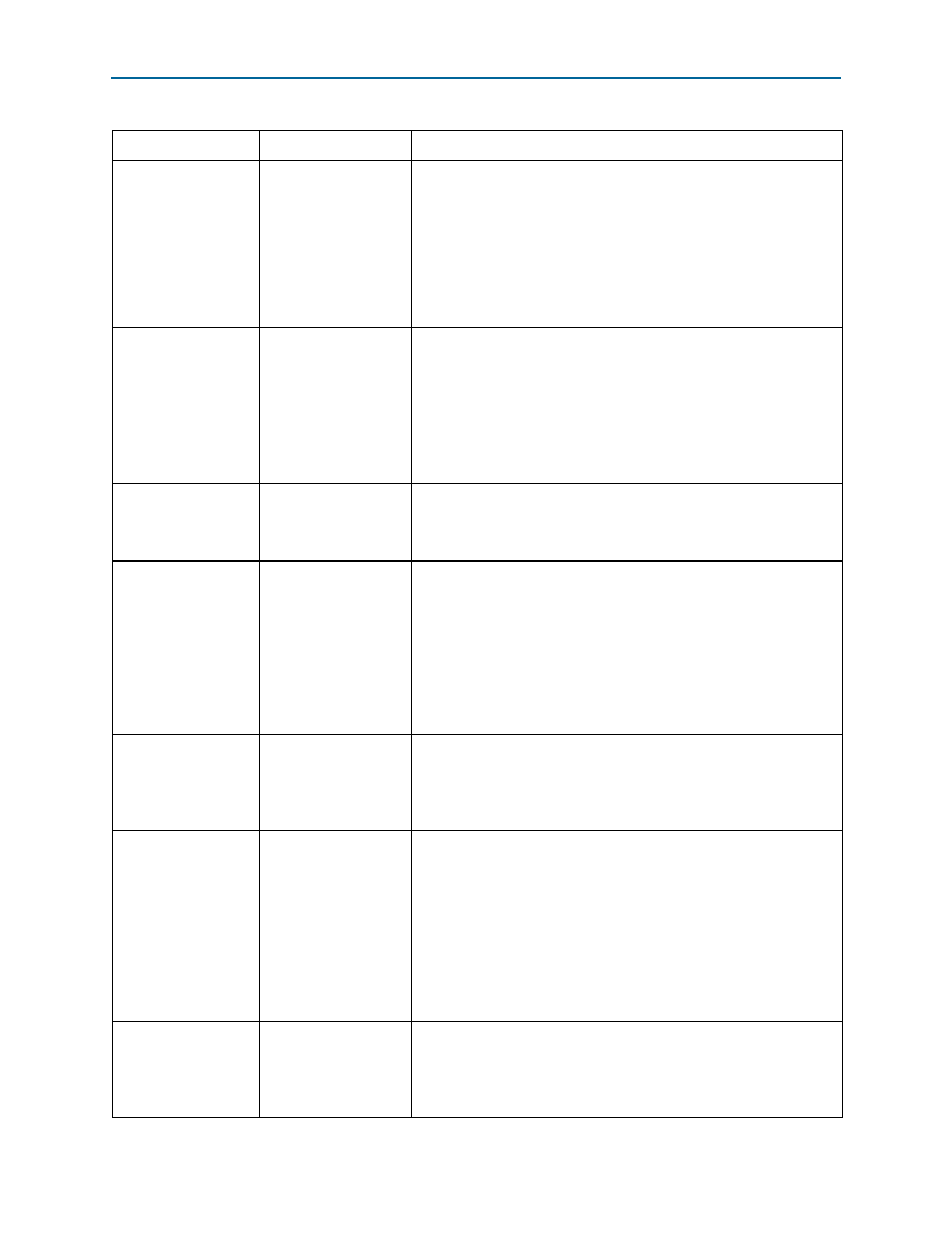

PHY interface

16-bit SDR,

16-bit SDR w/TxClk,

8-bit DDR,

8-bit DDR w/TxClk,

8-bit DDR/SDR

w/TXClk,

8 bit SDR,

8-bit SDR w/TxClk,

serial

Selects the specific type of external PHY interface based on the interface

datapath width and clocking mode. Refer to

for additional detail on specific PHY modes.

The PHY interface setting only applies to the soft IP implementation.

Configure transceiver

block

Clicking this button brings up the transceiver parameter editor, allowing

you to access a much greater subset of the transceiver parameters than

was available in earlier releases. The parameters that you can access are

different for the soft and hard IP versions of the IP Compiler for PCI

Express and may change from release to release.

For Arria II GX, Cyclone IV GX, Stratix II GX, and Stratix IV GX

transceivers, refer to the “Protocol Settings for PCI Express (PIPE)” in

an explanation of these settings.

Lanes

×1, ×2, ×4, ×8

Specifies the maximum number of lanes supported. The ×8 soft IP

configuration is only supported for Stratix II GX devices. For information

about ×8 support in hard IP configurations, refer to

.

Xcvr ref_clk

PHY pclk

100 MHz, 125 MHz

For Arria II GX, Cyclone IV GX, HardCopy IV GX, and Stratix IV GX, you

can select either a 100 MHz or 125 MHz reference clock for Gen1

operation; Gen2 requires a 100 MHz clock. The Arria GX and

Stratix II GX devices require a 100 MHz clock. If you use a PIPE

interface (and the PHY type is not Arria GX, Arria II GX, Cyclone IV GX,

HardCopy IV GX, Stratix II GX, or Stratix IV GX) the refclk is not

required.

For Custom and TI X101100 PHYs, the PHY pclk frequency is 125 MHz.

For the NXP PX1011A PHY, the pclk value is 250 MHz.

Application Interface

64-bit Avalon-ST,

128-bit Avalon-ST,

Descriptor/Data,

Avalon-MM

Specifies the interface between the PCI Express transaction layer and the

application layer. When using the parameter editor, this parameter can

be set to Avalon-ST or Descriptor/Data. Altera recommends the Avalon-

ST option for all new designs. 128-bit Avalon-ST is only available when

using the hard IP implementation.

Port type

Native Endpoint

Legacy Endpoint

Root Port

Specifies the port type. Altera recommends Native Endpoint for all new

endpoint designs. Select Legacy Endpoint only when you require I/O

transaction support for compatibility. The Qsys design flow only

supports Native Endpoint and the Avalon-MM interface to the user

application. The Root Port option is available in the hard IP

implementations.

The endpoint stores parameters in the Type 0 configuration space which

is outlined in

. The root port stores parameters in

the Type 1 configuration space which is outlined in

.

PCI Express version

1.0A, 1.1, 2.0

Selects the PCI Express specification with which the variation is

compatible. Depending on the device that you select, the IP Compiler for

PCI Express hard IP implementation supports PCI Express versions 1.1

and 2.0. The IP Compiler for PCI Express soft IP implementation

supports PCI Express versions 1.0a and 1.1

Table 3–9. System Settings Parameters (Part 3 of 4)

Parameter

Value

Description