Lmi read operation, Lmi write operation – Altera IP Compiler for PCI Express User Manual

Page 124

5–38

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

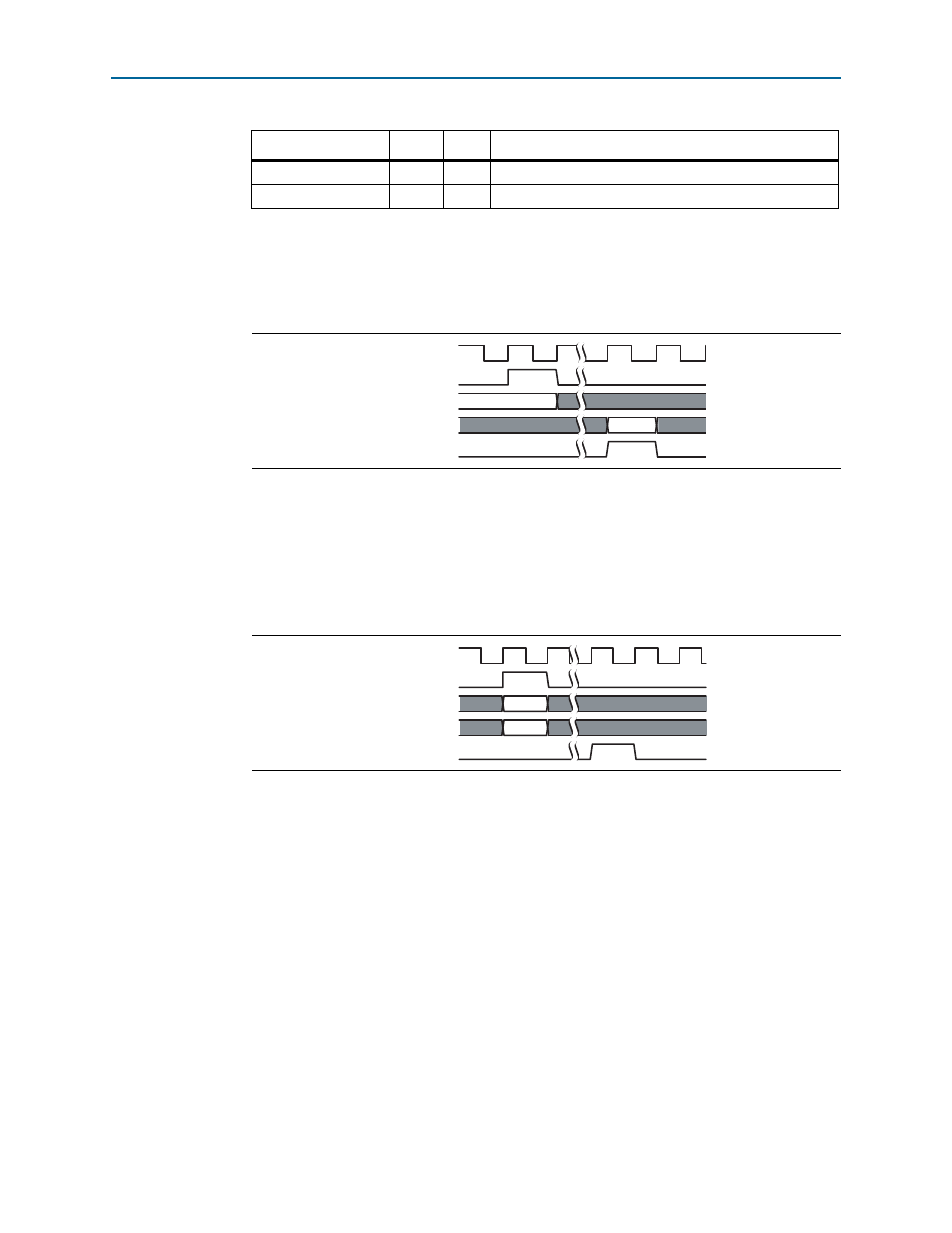

LMI Read Operation

illustrates the read operation. The read data remains available until the

next local read or system reset.

LMI Write Operation

illustrates the LMI write. Only writeable configuration bits are

overwritten by this operation. Read-only bits are not affected. LMI write operations

are not recommended for use during normal operation with the exception of AER

header logging.

IP Core Reconfiguration Block Signals—Hard IP Implementation

The IP Compiler for PCI Express reconfiguration block interface is implemented using

an Avalon-MM slave interface with an 8–bit address and 16–bit data. This interface is

available when you select Enable for the PCIe Reconfig option on the System

Settings

page of the IP Compiler for PCI Express parameter editor. You can use this

interface to change the value of configuration registers that are read-only at run time.

For a description of the registers available through this interface refer to

Reconfiguration and Offset Cancellation

lmi_addr

12

I

Address inputs, [1:0] not used

lmi_din

32

I

Data inputs

Figure 5–33. LMI Read

Figure 5–34. LMI Write

Table 5–17. LMI Interface

Signal

Width

Dir

Description

pld_clk

lmi_rden

lmi_addr[11:0]

lmi_dout[31:0]

lmi_ack

pld_clk

lmi_wren

lmi_din[31:0]

lmi_addr[11:0]

lmi_ack