Table 6–3 on, 0x050, 0x05c – Altera IP Compiler for PCI Express User Manual

Page 151: Table 6–3, For d, Table 6–4

Chapter 6: Register Descriptions

6–3

Configuration Space Register Content

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

describes the type 1 configuration settings.

describes the MSI capability structure.

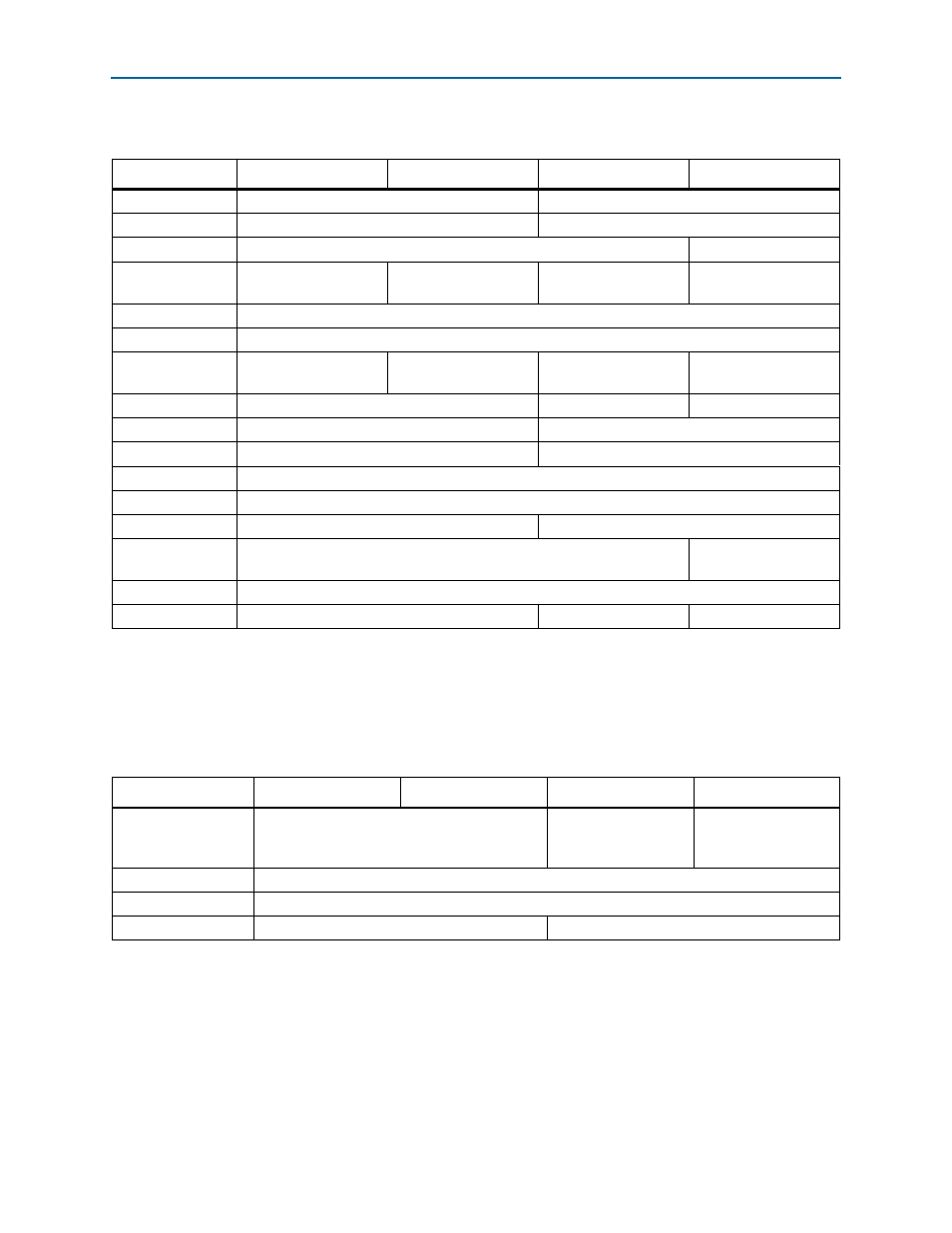

Table 6–3. PCI Type 1 Configuration Space Header (Root Ports) , Rev2 Spec: Type 1 Configuration Space Header

Byte Offset

31:24

23:16

15:8

7:0

0x0000

0x004

Status

Command

0x008

0x00C

BIST

Header Type

Primary Latency

Timer

Cache Line Size

0x010

0x014

0x018

Secondary Latency

Timer

Subordinate Bus

Number

Secondary Bus

Number

Primary Bus Number

0x01C

Secondary Status

I/O Limit

I/O Base

0x020

Memory Limit

Memory Base

0x024

Prefetchable Memory Limit

Prefetchable Memory Base

0x028

Prefetchable Base Upper 32 Bits

0x02C

Prefetchable Limit Upper 32 Bits

0x030

I/O Limit Upper 16 Bits

I/O Base Upper 16 Bits

0x034

Reserved

Capabilities

Pointer

0x038

Expansion ROM Base Address

0x03C

Bridge Control

Interrupt Pin

Interrupt Line

Note to

(1) Refer to

for a comprehensive list of correspondences between the configuration space registers and the

Table 6–4. MSI Capability Structure, Rev2 Spec: MSI and MSI-X Capability Structures

Byte Offset

31:24

23:16

15:8

7:0

0x050

Message Control

Configuration MSI Control Status Register Field

Next Cap Ptr

Capability ID

0x054

Message Address

0x058

Message Upper Address

0x05C

Reserved

Message Data

Note to

(1) Refer to

for a comprehensive list of correspondences between the configuration space registers and the