Release information – Altera IP Compiler for PCI Express User Manual

Page 5

Chapter 1: Datasheet

1–3

Release Information

August 2014

Altera Corporation

Release Information

provides information about this release of the IP Compiler for PCI Express.

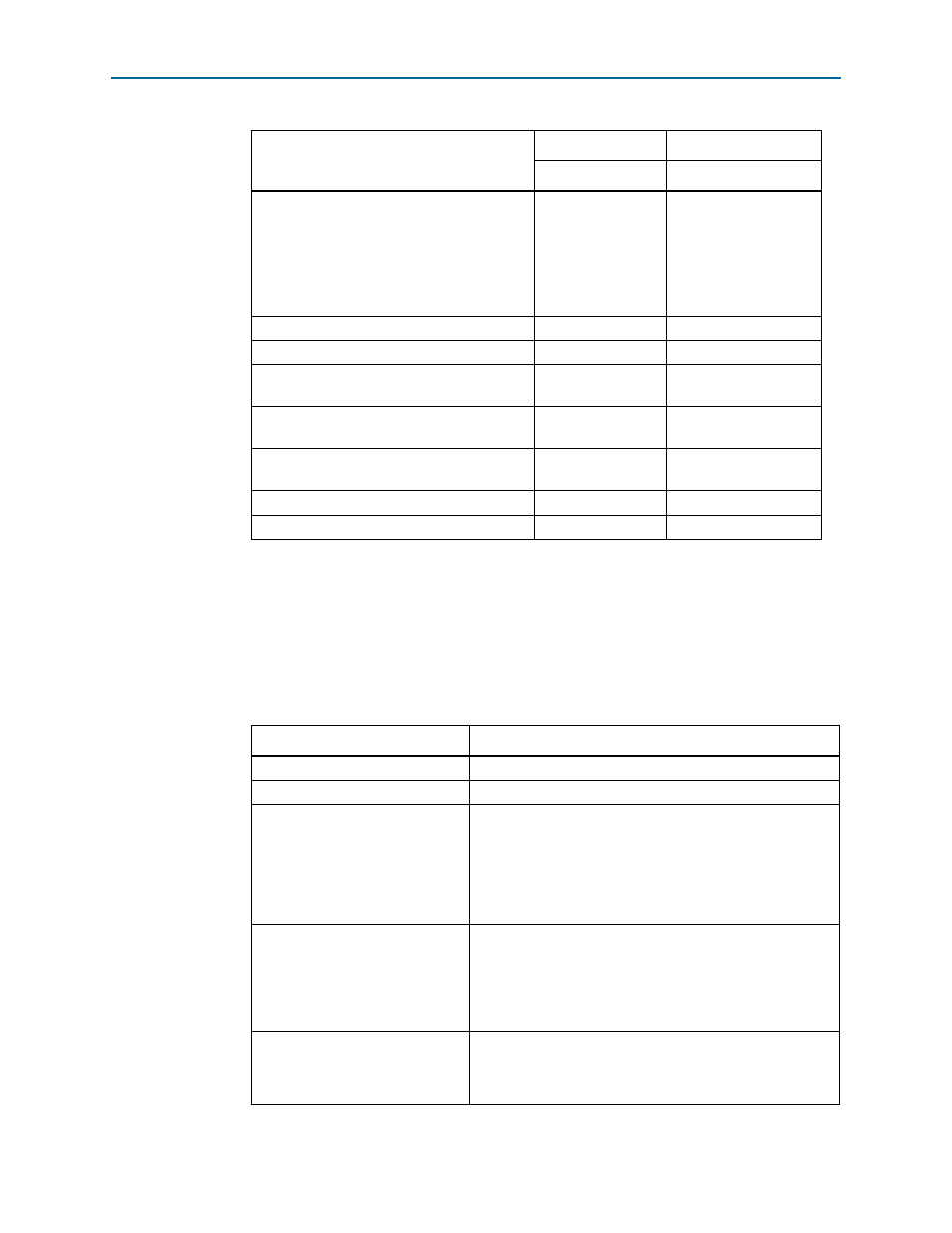

Transaction layer packet type (TLP)

■

Memory read

request

■

Memory write

request

■

Completion with

or without data

■

Memory read request

■

Memory write

request

■

Completion with or

without data

Maximum payload size

128–256 bytes

128–256 bytes

Number of virtual channels

1

1

Reordering of out–of–order completions

(transparent to the application layer)

Supported

Supported

Requests that cross 4 KByte address

boundary (transparent to the application layer)

Supported

Supported

Number of tags supported for non-posted

requests

16

16

ECRC forwarding on RX and TX

Not supported

Not supported

MSI-X

Not supported

Not supported

Notes to

(1) Not recommended for new designs.

(2) Refer to

Appendix A, Transaction Layer Packet (TLP) Header Formats

for the layout of TLP headers.

Table 1–2. IP Compiler for PCI Express Features (Part 2 of 2)

Feature

Hard IP

Soft IP

Table 1–3. IP Compiler for PCI Express Release Information

Item

Description

Version

14.0

Release Date

June 2014

Ordering Codes

IP-PCIE/1

IP-PCIE/4

IP-PCIE/8

IP-AGX-PCIE/1

IP-AGX-PCIE/4

No ordering code is required for the hard IP implementation.

Product IDs

■

Hard IP Implementation

■

Soft IP Implementation

FFFF

×1–00A9

×4–00AA

×8–00AB

Vendor ID

■

Hard IP Implementation

■

Soft IP Implementation

6AF7

6A66