Altera IP Compiler for PCI Express User Manual

Page 163

Chapter 6: Register Descriptions

6–15

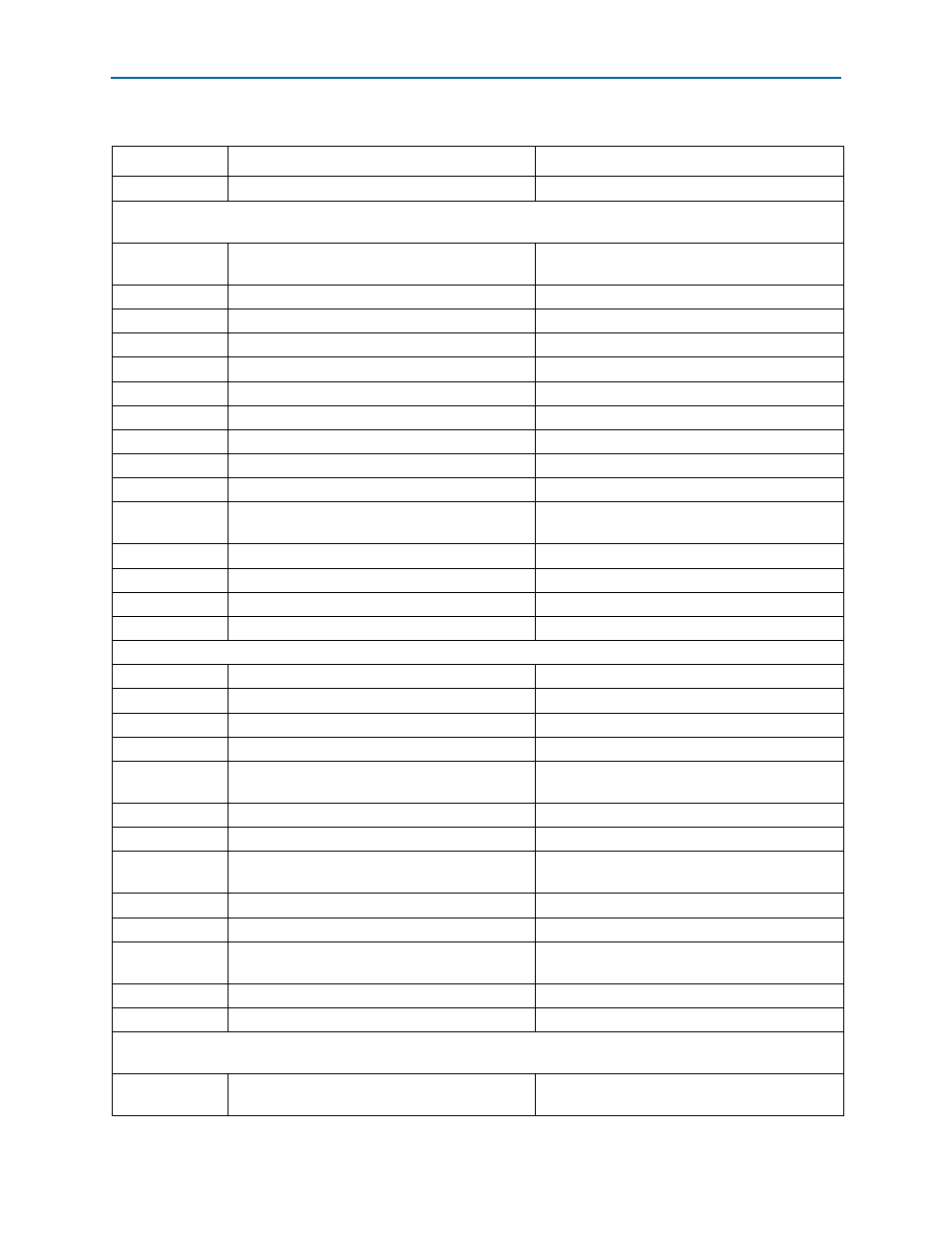

Comprehensive Correspondence between Config Space Registers and PCIe Spec Rev 2.0

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

0x0A0

Root Status

Root Status Register

0x080

PCI Express Capabilities Register Next Cap PTR

PCI Express Cap ID

PCI Express Capabilities Register /PCI Express

Capability List Register

0x084

Device capabilities

Device Capabilities Register

0x088

Device Status Device Control

Device Status Register / Device Control Register

0x08C

Link capabilities

Link Capabilities Register

0x090

Link Status Link Control

Link Status Register / Link Control Register

0x094

Slot Capabilities

Slot Capabilities Register

0x098

Slot Status Slot Control

Slot Status Register / Slot Control Register

0x09C

Root Capabilities Root Control

Root Capabilities Register / Root Control Register

0x0A0

Root Status

Root Status Register

0x0A4

Device Capabilities 2

Device Capabilities 2 Register

0x0A8

Device Status 2 Device Control 2

Device Status 2 Register / Device Control 2

Register

0x0AC

Link Capabilities 2

Link Capabilities 2 Register

0x0B0

Link Status 2 Link Control 2

Link Status 2 Register / Link Control 2 Register

0x0B4

Slot Capabilities 2

Slot Capabilities 2 Register

0x0B8

Slot Status 2 Slot Control 2

Slot Status 2 Register / Slot Control 2 Register

Table 6-9.

Virtual Channel Capability Structure, Rev2 Spec: Virtual Channel Capability

0x100

Next Cap PTR Vers. Extended Cap ID

Virtual Channel Enhanced Capability Header

0x104

ReservedP Port VC Cap 1

Port VC Capability Register 1

0x108

VAT offset ReservedP VC arbit. cap

Port VC Capability Register 2

0x10C

Port VC Status Port VC control

Port VC Status Register / Port VC Control Register

0x110

PAT offset 0 (31:24) VC Resource Capability

Register (0)

VC Resource Capability Register

0x114

VC Resource Control Register (0)

VC Resource Control Register

0x118

VC Resource Status Register (0) ReservedP

VC Resource Status Register

0x11C

PAT offset 1 (31:24) VC Resource Capability

Register (1)

VC Resource Capability Register

0x120

VC Resource Control Register (1)

VC Resource Control Register

0x124

VC Resource Status Register (1) ReservedP

VC Resource Status Register

0x164

PAT offset 7 (31:24) VC Resource Capability

Register (7)

VC Resource Capability Register

0x168

VC Resource Control Register (7)

VC Resource Control Register

0x16C

VC Resource Status Register (7) ReservedP

VC Resource Status Register

0x800

PCI Express Enhanced Capability Header

Advanced Error Reporting Enhanced Capability

Header

Table 6–23. Correspondence Configuration Space Registers and PCIe Base Specification Rev. 2.0 Description (Part 4

of 5)

Byte Address

Config Reg Offset 31:24 23:16 15:8 7:0

Corresponding Section in PCIe Specification