Physical layer interface signals, Transceiver control signals – Altera IP Compiler for PCI Express User Manual

Page 139

Chapter 5: IP Core Interfaces

5–53

Physical Layer Interface Signals

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Physical Layer Interface Signals

This section describes the global PHY support signals which are only present in

variations that target an Arria II GX, Arria II GZ, Cyclone IV GX, or Stratix IV GX

device and use an integrated PHY. When selecting an integrated PHY, the parameter

editor generates a SERDES variation file,

to the IP core variation file,

Transceiver Control Signals

describes the transceiver support signals.

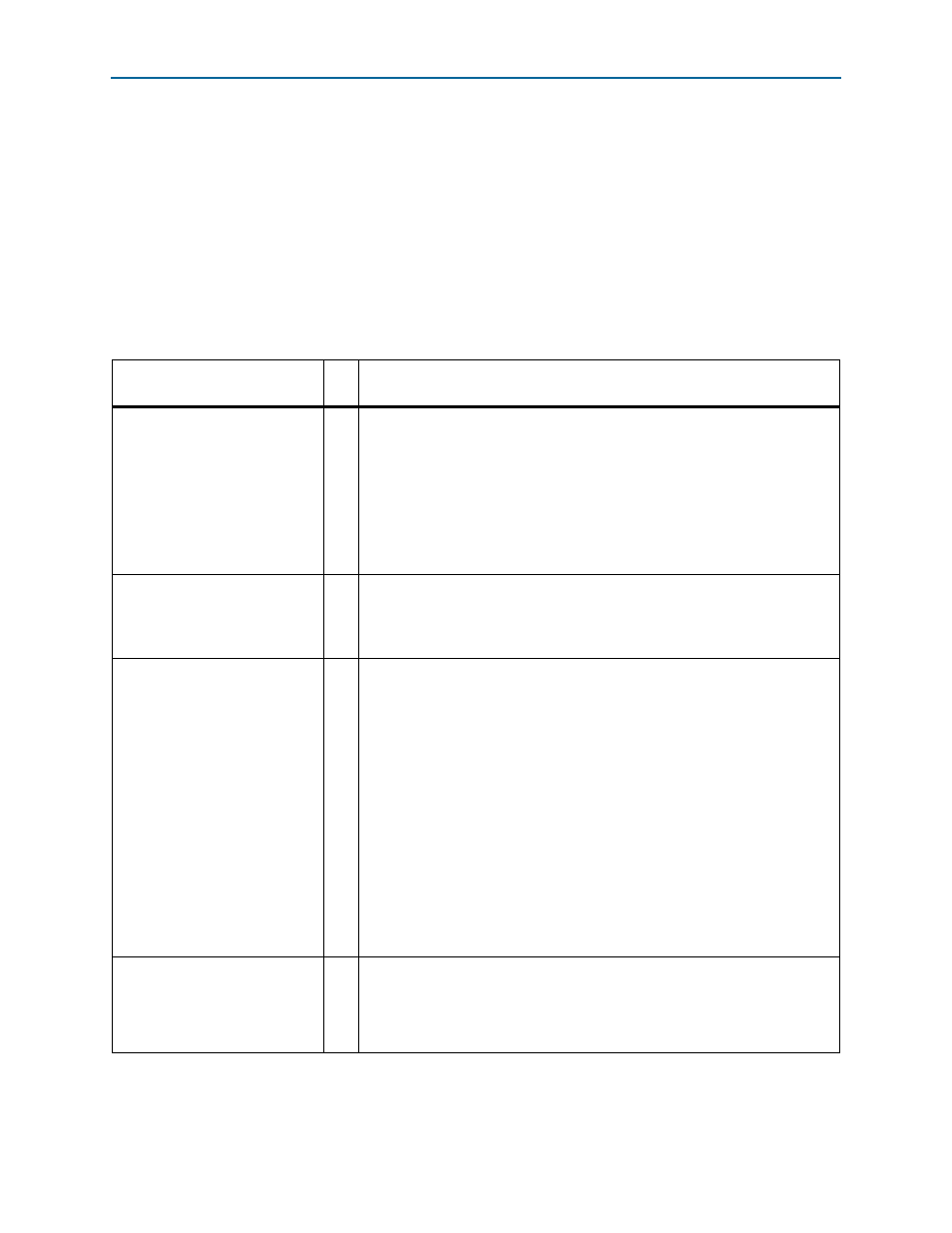

Table 5–28. Transceiver Control Signals (Part 1 of 2)

Signal Name in

Qsys

I/O

Description

cal_blk_clk

/cal_blk_clk_clk

I

The cal_blk_clk input signal is connected to the transceiver calibration block

clock (cal_blk_clk) input. All instances of transceivers in the same device

must have their cal_blk_clk inputs connected to the same signal because

there is only one calibration block per device. This input should be connected to a

clock operating as recommended by the

,

the

, or th

chapter in volume 2 of the Arria II GX Device Handbook. Connection information

is also provided in

gxb_powerdown/

pipe_ext_gxb_powerdown

I

The gxb_powerdown signal connects to the transceiver calibration block

gxb_powerdown input. This input should be connected as recommended by the

r volume 2 of the

When the calibration clock is not used, this input must be tied to ground.

reconfig_fromgxb[16:0]

(Stratix IV GX ×1 and ×4)

reconfig_fromgxb[33:0]

(Stratix IV GX ×8)

reconfig_togxb[3:0]

(Stratix IV GX)

reconfig_clk

(Arria II GX, Arria II GZ,

Cyclone IV GX)/

reconfig_gxbclk_clk

O

O

I

I

I

These are the transceiver dynamic reconfiguration signals. These signals may be

used for cases in which the IP Compiler for PCI Express instance shares a

transceiver quad with another protocol that supports dynamic reconfiguration.

They may also be used in cases in which the transceiver analog controls (V

OD

,

pre-emphasis, and manual equalization) must be modified to compensate for

extended PCI Express interconnects such as cables. In these cases, these signals

must be connected as described in the

wise,

when unused, the reconfig_clk signal should be tied low, reconfig_togxb

should be tied to b'010, and reconfig_fromgxb should be left open.

For Arria II GX and Stratix IV GX devices, dynamic reconfiguration is required for

IP Compiler for PCI Express designs to compensate for variations due to

process, voltage and temperature. You must connect the ALTGX_RECONFIG

instance to the ALTGX instances with receiver channels in your design using

these signals. The maximum frequency of reconfig_clk is 50 MHz. For more

information about instantiating the ALTGX_RECONFIG megafunction in your

design refer to

“Transceiver Offset Cancellation” on page 13–9

.

fixedclk_serdes

I

A 125 MHz free running clock that you must provide that serves as input to the

fixed clock of the transceiver. fixedclk_serdes and the 50 MHz

reconfig_clk

must be free running and not derived from refclk. This signal

is used in the hard IP implementation for Arria II GX, Arria II GZ, Cyclone IV GX,

HardCopy IV GX, and Stratix IV GX devices.