Altera IP Compiler for PCI Express User Manual

Page 63

Chapter 4: IP Core Architecture

4–5

Application Interfaces

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

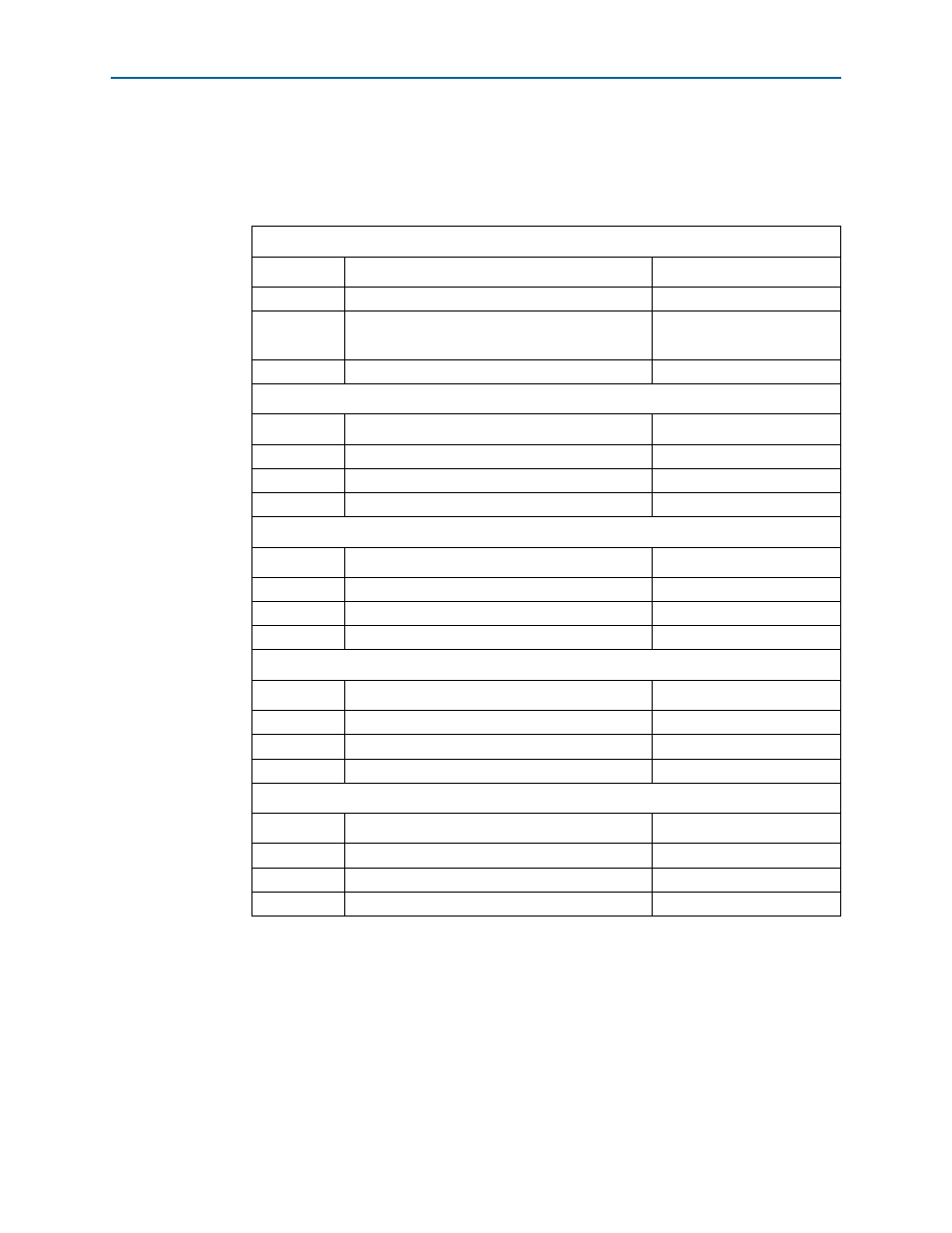

provides the application clock frequencies for the hard IP and soft IP

implementations. As this table indicates, the Avalon-ST interface can be either 64 or

128 bits for the hard IP implementation. For the soft IP implementation, the Avalon-ST

interface is 64 bits.

The following sections introduce the functionality of the interfaces shown in

. For more detailed information, refer to

Avalon-ST RX Port” on page 5–6

“64- or 128-Bit Avalon-ST TX Port” on page 5–15

.

Table 4–1. Application Clock Frequencies

Hard IP Implementation— Stratix IV GX and Hardcopy IV GX Devices

Lanes

Gen1

Gen2

×1

62.5 MHz @ 64 bits

or 125 MHz @ 64 bits

125 MHz @ 64 bits

×4

125 MHz @ 64 bits

250 MHz @ 64 bits or

125 MHz @ 128 bits

×8

250 MHz @ 64 bits or 125 MHz @ 128 bits

250 MHz @ 128 bits

Hard IP Implementation—Arria II GX Devices

Lanes

Gen1

Gen2

×1

62.5 MHz @ 64 bits

or 125 MHz @ 64 bits

—

×4

125 MHz @ 64 bits

—

×8

125 MHz @ 128 bits

—

Hard IP Implementation—Arria II GZ Devices

Lanes

Gen1

Gen2

×1

62.5 MHz @ 64 bits

or 125 MHz @ 64 bits

125 MHz @ 64 bits

×4

125 MHz @ 64 bits

125 MHz @ 128 bits

×8

125 MHz @ 128 bits

—

Hard IP Implementation—Cyclone IV GX Devices

Lanes

Gen1

Gen2

×1

62.5 MHz @ 64 bits or 125 MHz @ 64 bits

—

×2

125 MHz @ 64 bits

—

×4

125 MHz @ 64 bits

—

Soft IP Implementation

Lanes

Gen1

Gen2

×1

62.5 MHz @ 64 bits or125 MHz @64 bits

—

×4

125 MHz @ 64 bits

—

×8

250 MHz @ 64 bits

—

Notes to

(1) The 62.5 MHz application clock is available in parameter editor-generated Gen1:×1 hard IP implementations in any

device.