System settings, Pci base address registers – Altera IP Compiler for PCI Express User Manual

Page 38

3–2

Chapter 3: Parameter Settings

Parameters in the Qsys Design Flow

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

System Settings

The first parameter section of the IP Compiler for PCI Express parameter editor in the

Qsys flow contains the parameters for the overall system settings.

describes

these settings.

PCI Base Address Registers

The ×1 and ×4 IP cores support memory space BARs ranging in size from 128 bytes to

the maximum allowed by a 32-bit or 64-bit BAR. The ×8 IP cores support memory

space BARs from 4 KBytes to the maximum allowed by a 32-bit or 64-bit BAR.

The available BARs reflect the fact that the Qsys design flow supports only native

endpoints, with no support for I/O space BARs or 32-bit prefetchable memory.

The Avalon-MM address is the translated base address corresponding to a BAR hit of

a received request from the PCI Express link.

In the Qsys design flow, the PCI Base Address Registers (Type 0 Configuration

Space)

Bar Size and Avalon Base Address information populates from Qsys. You

cannot enter this information in the IP Compiler for PCI Express parameter editor.

After you set the base addresses in Qsys, either automatically or by entering them

manually, the values appear when you reopen the parameter editor.

Altera recommends using the Qsys option—on the System menu, click Assign Base

Addresses

—to set the base addresses automatically. If you decide to enter the address

translation entries manually, then you must avoid conflicts in address assignment

when adding other components, making interconnections, and assigning base

addresses.

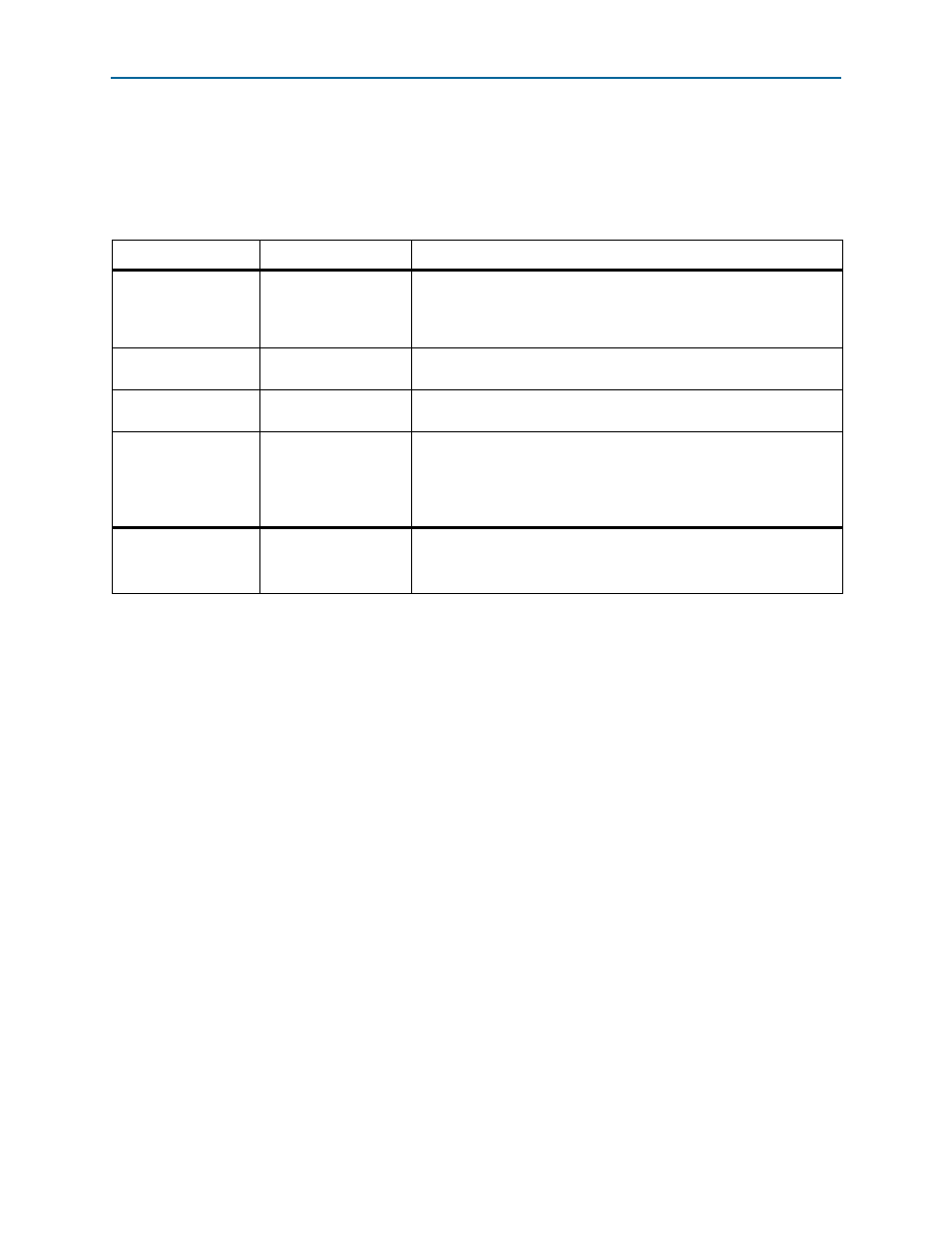

Table 3–1. Qsys Flow System Settings Parameters

Parameter

Value

Description

Gen2 Lane Rate Mode

Off/On

Specifies the maximum data rate at which the link can operate. Turning

on Gen2 Lane Rate Mode sets the Gen2 rate, and turning it off sets the

Gen1 rate. Refer to

for a complete list of Gen1

and Gen2 support.

Number of Lanes

×1, ×2, ×4, ×8

Specifies the maximum number of lanes supported. Refer to

for a complete list of device support for numbers of lanes.

Reference clock

frequency

100 MHz, 125 MHz

You can select either a 100 MHz or 125 MHz reference clock for Gen1

operation; Gen2 requires a 100 MHz clock.

Use 62.5 MHz

application clock

Off/On

Specifies whether the application interface clock operates at the slower

62.5 MHz frequency to support power saving. This parameter can only

be turned on for some Gen1 ×1 variations. Refer to

Table 4–1 on

page 4–4

for a list of the supported application interface clock

frequencies in different device families.

Test out width

None, 9 bits, or 64 bits

Indicates the width of the test_out signal. Most of these signals are

reserved. Refer to

for more information.

Altera recommends that you configure the 64-bit width.