Recommended speed grades – Altera IP Compiler for PCI Express User Manual

Page 13

Chapter 1: Datasheet

1–11

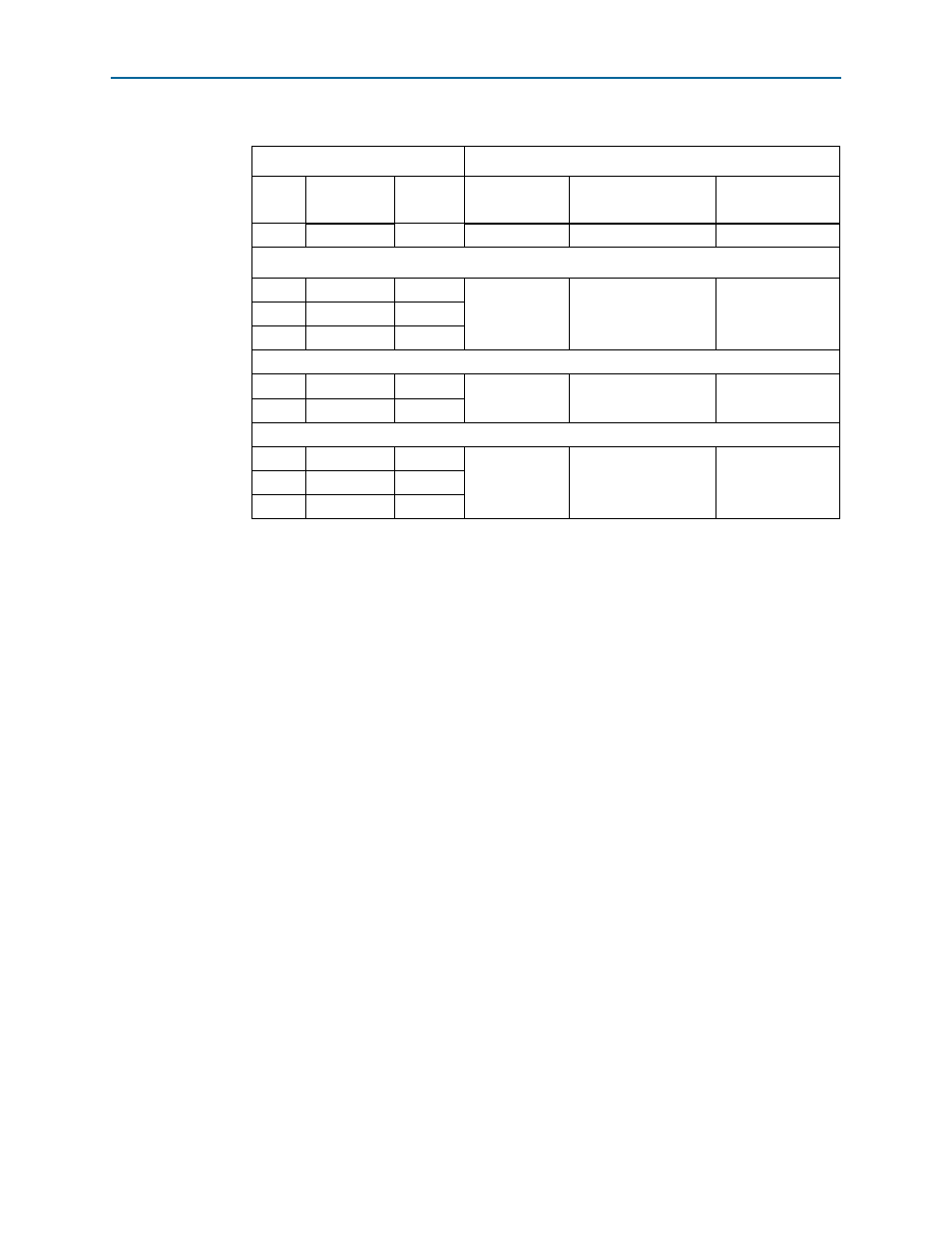

Recommended Speed Grades

August 2014

Altera Corporation

f

Refer to

Appendix C, Performance and Resource Utilization Soft IP Implementation

for performance and resource utilization for the soft IP implementation.

Recommended Speed Grades

shows the recommended speed grades for each device family for the

supported link widths and internal clock frequencies. For soft IP implementations of

the IP Compiler for PCI Express, the table lists speed grades that are likely to meet

timing; it may be possible to close timing in a slower speed grade. For the hard IP

implementation, the speed grades listed are the only speed grades that close timing.

When the internal clock frequency is 125 MHz or 250 MHz, Altera recommends

setting the Quartus II Analysis & Synthesis Settings Optimization Technique to

Speed

.

×4

125

1

Avalon-MM Interface–Qsys Design Flow

×1

125

1

1600

1600

18

×4

125

1

×8

250

1

Avalon-MM Interface–Qsys Design Flow - Completer Only

×1

125

1

1000

1150

10

×4

125

1

Avalon-MM Interface–Qsys Design Flow - Completer Only Single Dword

×1

125

1

430

450

0

×4

125

1

×4

250

1

Note to

:

(1) The transaction layer of the Avalon-MM implementation is implemented in programmable logic to improve latency.

Table 1–8. Performance and Resource Utilization in Arria II GX, Arria II GZ, Cyclone IV GX, and

Stratix IV GX Devices (Part 2 of 2)

Parameters

Size

Lane

Width

Internal

Clock (MHz)

Virtual

Channel

Combinational

ALUTs

Dedicated

Registers

Memory Blocks

M9K