Configuration space signals—soft ip implementation – Altera IP Compiler for PCI Express User Manual

Page 122

5–36

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Configuration Space Signals—Soft IP Implementation

The signals in

reflect the current values of several configuration space

registers that the application layer may need to access. These signals are available in

configurations using the Avalon-ST interface (soft IP implementation) or the

descriptor/data interface.

cfg_tcvcmap

24

O

Configuration traffic class (TC)/virtual channel (VC) mapping. The

application layer uses this signal to generate a transaction layer

packet mapped to the appropriate virtual channel based on the

traffic class of the packet.

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0).

cfg_tcvcmap[5:3]

: Mapping for TC1.

cfg_tcvcmap[8:6]

: Mapping for TC2.

cfg_tcvcmap[11:9]

: Mapping for TC3.

cfg_tcvcmap[14:12]

: Mapping for TC4.

cfg_tcvcmap[17:15]

: Mapping for TC5.

cfg_tcvcmap[20:18]

: Mapping for TC6.

cfg_tcvcmap[23:21]

: Mapping for TC7.

cfg_busdev

13

O

Bus/device number captured by or programmed in the core.

0x08

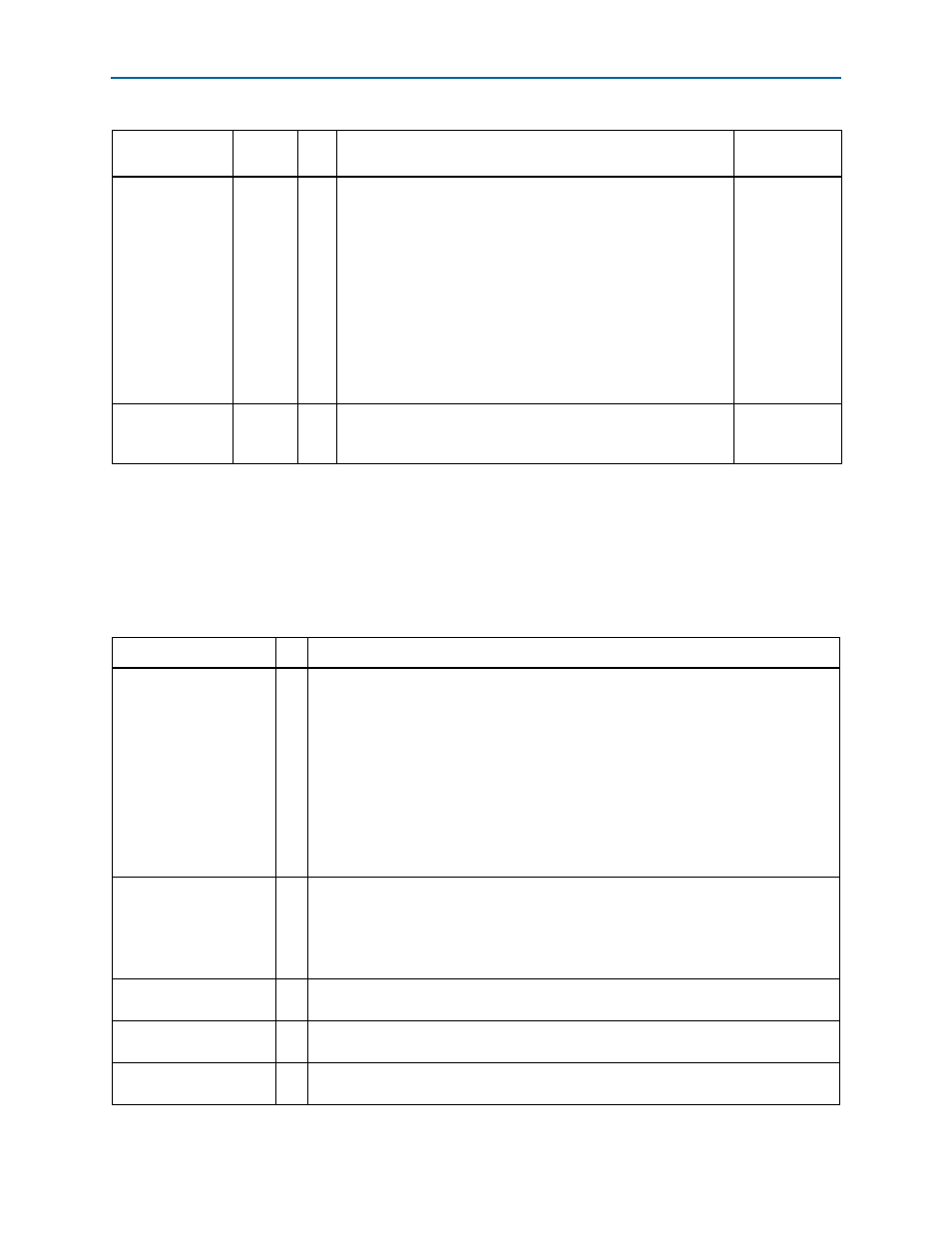

Table 5–15. Configuration Space Register Descriptions (Part 3 of 3)

Register

Width

Dir

Description

Register

Reference

Table 5–16. Configuration Space Signals (Soft IP Implementation)

Signal

I/O

Description

cfg_tcvcmap[23:0]

O

Configuration traffic class/virtual channel mapping: The application layer uses this signal

to generate a transaction layer packet mapped to the appropriate virtual channel based on

the traffic class of the packet.

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0).

cfg_tcvcmap[5:3]

: Mapping for TC1.

cfg_tcvcmap[8:6]

: Mapping for TC2.

cfg_tcvcmap[11:9]

: Mapping for TC3.

cfg_tcvcmap[14:12]

: Mapping for TC4.

cfg_tcvcmap[17:15]

: Mapping for TC5.

cfg_tcvcmap[20:18]

: Mapping for TC6.

cfg_tcvcmap[23:21]

: Mapping for TC7.

cfg_busdev[12:0]

O

Configuration bus device: This signal generates a transaction ID for each transaction layer

packet, and indicates the bus and device number of the IP core. Because the IP core only

implements one function, the function number of the transaction ID must be set to 000b.

cfg_busdev[12:5]

: Bus number.

cfg_busdev[4:0]

: Device number.

cfg_prmcsr[31:0]

O

Configuration primary control status register. The content of this register controls the PCI

status.

cfg_devcsr[31:0]

O

Configuration device control status register. Refer to the

for details.

cfg_linkcsr[31:0]

O

Configuration link control status register. Refer to the

for

details.