Reset and link training signals – Altera IP Compiler for PCI Express User Manual

Page 110

5–24

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

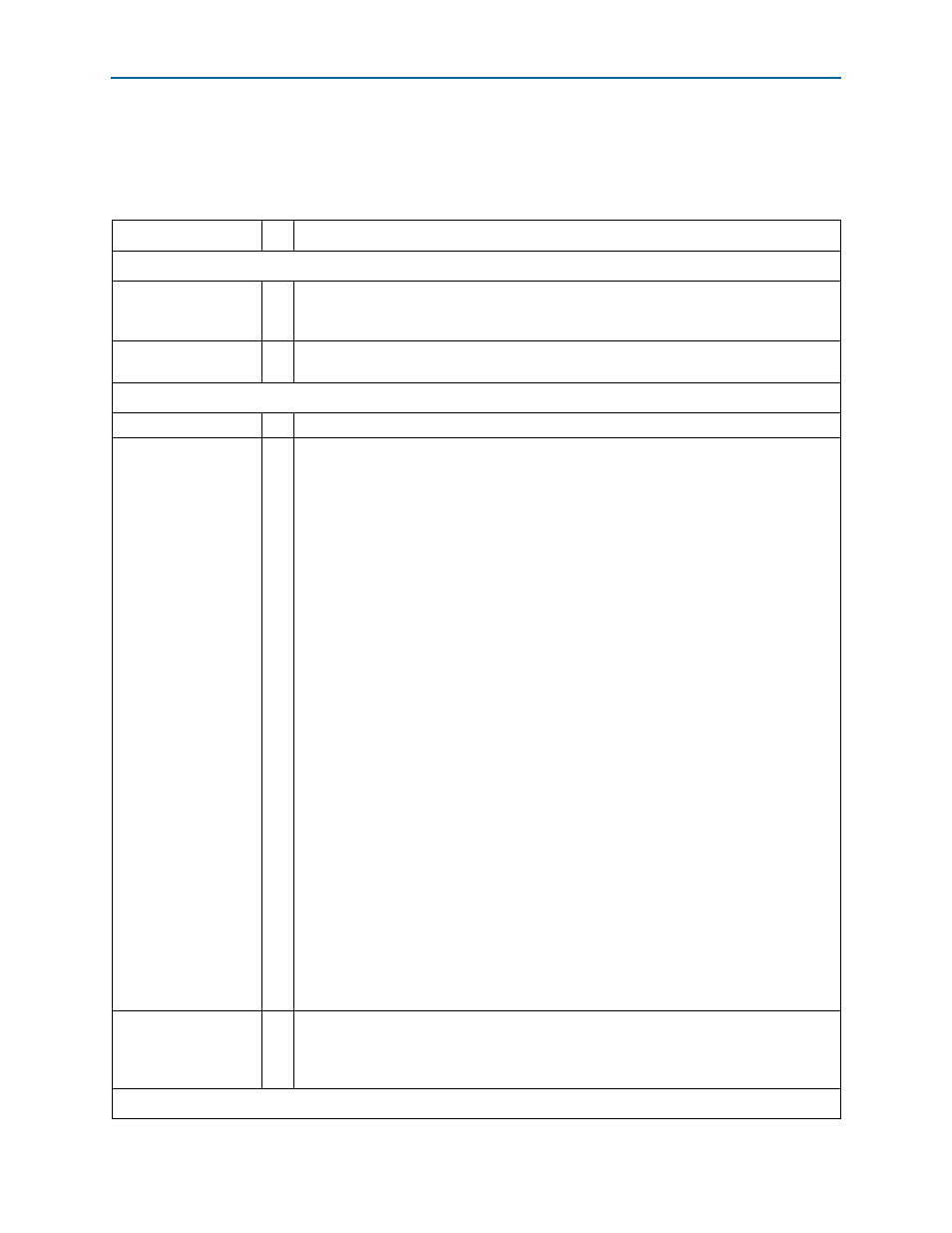

Reset and Link Training Signals

describes the reset signals available in configurations using the Avalon-ST

interface or descriptor/data interface.

Table 5–7. Reset and Link Training Signals (Part 1 of 2)

Signal

I/O

Description

pcie_rstn

I

pcie_rstn

directly resets all sticky IP Compiler for PCI Express configuration registers.

Sticky registers are those registers that fail to reset in L2 low power mode or upon a

fundamental reset. This is an asynchronous reset.

local_rstn

I

reset_n

is the system-wide reset which resets all IP Compiler for PCI Express circuitry not

affected by pcie_rstn. This is an asynchronous reset.

Both

suc_spd_neg

O

Indicates successful speed negotiation to Gen2 when asserted.

ltssm[4:0]

O

LTSSM state: The LTSSM state machine encoding defines the following states:

■

00000: detect.quiet

■

00001: detect.active

■

00010: polling.active

■

00011: polling.compliance

■

00100: polling.configuration

■

00101: polling.speed

■

00110: config.linkwidthstart

■

00111: config.linkaccept

■

01000: config.lanenumaccept

■

01001: config.lanenumwait

■

01010: config.complete

■

01011: config.idle

■

01100: recovery.rcvlock

■

01101: recovery.rcvconfig

■

01110: recovery.idle

■

01111: L0

■

10000: disable

■

10001: loopback.entry

■

10010: loopback.active

■

10011: loopback.exit

■

10100: hot.reset

■

10110: L1.entry

■

10111: L1.idle

■

11000: L2.idle

■

11001: L2.transmit.wake

■

11010: speed.recovery

reset_status

O

Reset Status signal. When asserted, this signal indicates that the IP core is in reset. This

signal is only available in the hard IP implementation. When the npor signal asserts,

reset_status

is reset to zero. The reset_status signal is synchronous to the pld_clk

and is deasserted only when the pld_clk is good.