External phys, External phy support, Bit sdr mode – Altera IP Compiler for PCI Express User Manual

Page 221: Refer to, Chapter 14, external phys

August 2014

Altera Corporation

IP Compiler for PCI Express U

14. External PHYs

External PHY Support

This chapter discusses external PHY support, which includes the external PHYs and

interface modes shown in

. The external PHY is not applicable to the hard

IP implementation.

When an external PHY is selected, additional logic required to connect directly to the

external PHY is included in the <variation name> module or entity.

The user logic must instantiate this module or entity in the design. The

implementation details for each of these modes are discussed in the following

sections.

16-bit SDR Mode

The implementation of this 16-bit SDR mode PHY support is shown in

and is included in the file <variation name>.v or <variation name>.vhd and includes a

PLL. The PLL inclock is driven by refclk and has the following outputs:

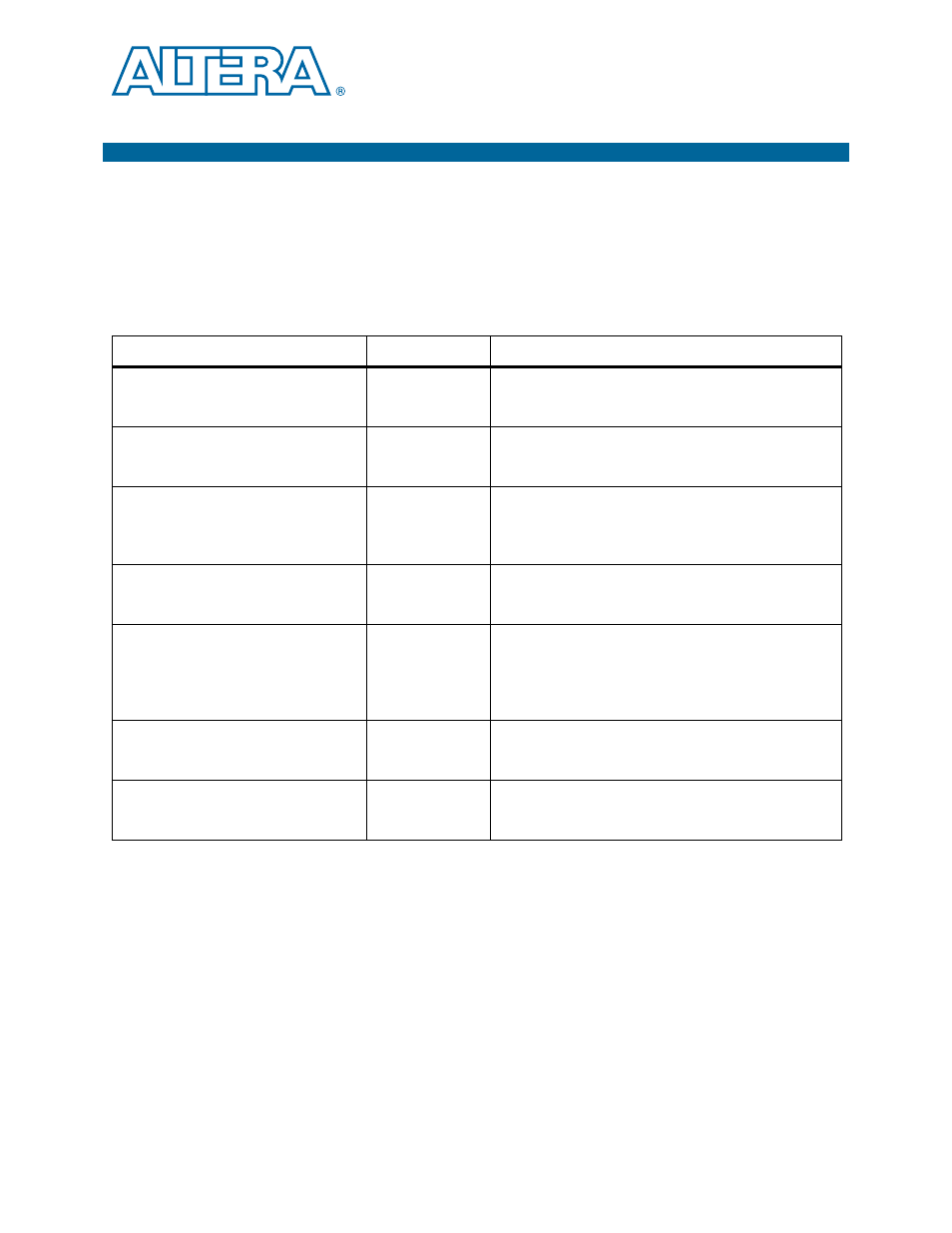

Table 14–1. External PHY Interface Modes

PHY Interface Mode

Clock Frequency

Notes

16-bit SDR

125 MHz

In this the generic 16-bit PIPE interface, both the TX and

RX

data are clocked by the refclk input which is the pclk

from the PHY.

16-bit SDR mode (with source

synchronous transmit clock)

125 MHz

This enhancement to the generic PIPE interface adds a

TXClk

to clock the TXData source synchronously to the

external PHY. The TIXIO1100 PHY uses this mode.

8-bit DDR

125 MHz

This double data rate version saves I/O pins without

increasing the clock frequency. It uses a single refclk input

(which is the pclk from the PHY) for clocking data in both

directions.

8-bit DDR mode (with 8-bit DDR source

synchronous transmit clock)

125 MHz

This double data rate version saves I/O pins without

increasing the clock frequency. A TXClk clocks the data

source synchronously in the transmit direction.

8-bit DDR/SDR mode (with 8-bit DDR

source synchronous transmit clock)

125 MHz

This is the same mode as 8-bit DDR mode except the

control signals rxelecidle, rxstatus, phystatus, and

rxvalid

are latched using the SDR I/O register rather

than the DDR I/O register. The TIXIO1100 PHY uses this

mode.

8-bit SDR

250 MHz

This is the generic 8-bit PIPE interface. Both the TX and RX

data are clocked by the refclk input which is the pclk from

the PHY. The NXP PX1011A PHY uses this mode.

8-bit SDR mode (with Source

Synchronous Transmit Clock)

250 MHz

This enhancement to the generic PIPE interface adds a

TXClk

to clock the TXData source synchronously to the

external PHY.

August 2014