External phy constraint support – Altera IP Compiler for PCI Express User Manual

Page 231

Chapter 14: External PHYs

14–11

External PHY Constraint Support

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

■

Select the type of interface to the PHY by selecting Custom in the PHY type list.

Several PHYs have multiple interface modes.

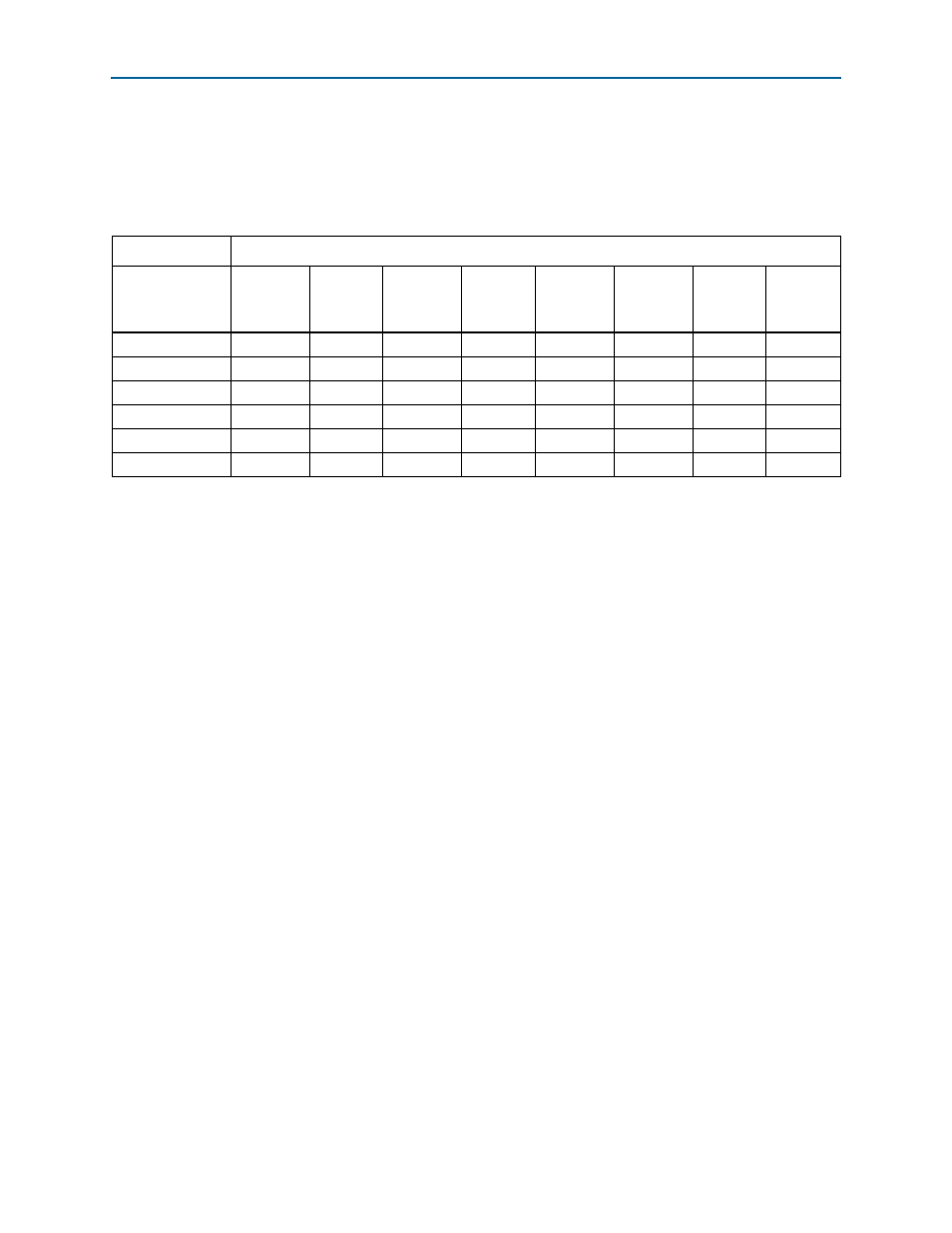

summarizes the PHY support matrix. For every supported PHY type and

interface, the table lists the allowed lane widths.

The TI XIO1100 device has some additional control signals that need to be driven by

your design. These can be statically pulled high or low in the board design, unless

additional flexibility is needed by your design and you want to drive them from the

Altera device. These signals are shown in the following list:

■

P1_SLEEP

must be pulled low. The IP Compiler for PCI Express requires the refclk

(RX_CLK from the XIO1100) to remain active while in the P1 powerdown state.

■

DDR_EN

must be pulled high if your variation of the IP Compiler for PCI Express

uses the 8-bit DDR (w/TXClk) mode. It must be pulled low if the 16-bit SDR

(w/TXClk) mode is used.

■

CLK_SEL

must be set correctly based on the reference clock provided to the

XIO1100. Consult the XIO1100 data sheet for specific recommendations.

External PHY Constraint Support

The IP Compiler for PCI Express supports various location and timing constraints.

When you parameterize and generate your IP core, the Quartus II software creates a

Tcl file that runs when you compile your design. The Tcl file incorporates the

following constraints that you specify when you parameterize and generate during

parameterization.

■

refclk

(pclk from the PHY) frequency constraint (125 MHz or 250 MHz)

■

Setup and hold constraints for the input signals

■

Clock-to-out constraints for the output signals

■

I/O interface standard

Altera also provides an SDC file with the same constraints. The TimeQuest timing

analyzer uses the SDC file.

1

You may need to modify the timing constraints to take into account the specific

constraints of your external PHY and your board design.

Table 14–4. External PHY Support Matrix

PHY Type

Allowed Interfaces and Lanes

16-bit

SDR

(pclk only)

16-bit

SDR

(w/TXClk)

8-bit

DDR

(pclk only)

8-bit

DDR

(w/TXClk)

8-bit

DDR/SDR

(w/TXClk)

8-bit

SDR

(pclk only)

8-bit

SDR

(w/TXClk)

Serial

Interface

Arria GX

-

-

-

-

-

-

-

×1, ×4

Stratix II GX

-

-

-

-

-

-

-

×1, ×4, ×8

Stratix IV GX

-

-

-

-

-

-

-

×1, ×4, ×8

TI XIO1100

-

×1

-

-

×1

-

-

-

NXP PX1011A

-

-

-

-

-

-

×1

-

Custom

×1, ×4

×1, ×4

×1, ×4

×1, ×4

-

×1, ×4

×1, ×4

-