Altera IP Compiler for PCI Express User Manual

Page 213

Chapter 13: Reconfiguration and Offset Cancellation

13–3

Dynamic Reconfiguration

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

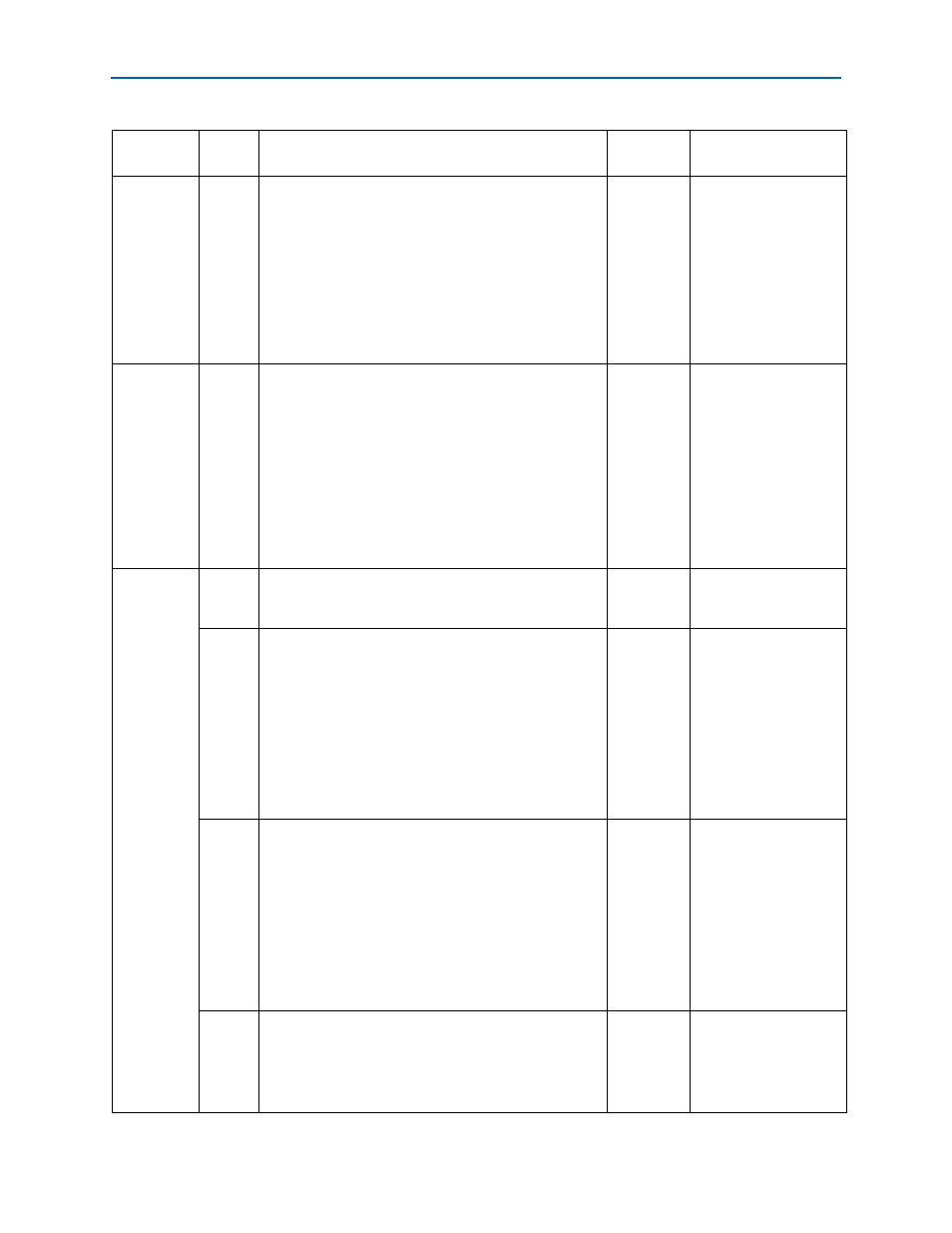

3

Surprise Down error reporting capabilities.

b’0

Link Capability register

(Available in PCI Express Base Specification Revision 1.1

compliant Cores, only.)

Downstream Port

. This bit must be set to 1 if the

component supports the optional capability of detecting

and reporting a Surprise Down error condition.

Upstream Port

. For upstream ports and components

that do not support this optional capability, this bit must

be hardwired to 0.

4

Data Link Layer active reporting capabilities.

b’0

Link Capability register

(Available in PCI Express Base Specification Revision 1.1

compliant Cores, only.)

Downstream Port: This bit must be set to 1 if the

component supports the optional capability of reporting

the DL_Active state of the Data Link Control and

Management state machine.

Upstream Port: For upstream ports and components that

do not support this optional capability, this bit must be

hardwired to 0.

5 Extended TAG field supported.

b’0

Device Capability

register

8:6

Endpoint L0s acceptable latency. The following encodings

are defined:

b’000 – Maximum of 64 ns.

b’001 – Maximum of 128 ns.

b’010 – Maximum of 256 ns.

b’011 – Maximum of 512 ns.

b’100 – Maximum of 1 µs.

b’101 – Maximum of 2 µs.

b’110 – Maximum of 4 µs.

b’111– No limit.

b’000

Device Capability

register

11:9

Endpoint L1 acceptable latency. The following encodings

are defined:

b’000 – Maximum of 1 µs.

b’001 – Maximum of 2 µs.

b’010 – Maximum of 4 µs.

b’011 – Maximum of 8 µs.

b’100 – Maximum of 16 µs.

b’101 – Maximum of 32 µs.

b’110 – Maximum of 64 µs.

b’111 – No limit.

b’000

Device Capability

register

14:12

These bits record the presence or absence of the attention

and power indicators.

b’000

Slot Capability register

[0]: Attention button present on the device.

[1]: Attention indicator present for an endpoint.

[2]: Power indicator present for an endpoint.

Table 13–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 2 of 7)

Address

Bits

Description

Default

Value

Additional Information