Altera IP Compiler for PCI Express User Manual

Page 120

5–34

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

describes the configuration space registers referred to in

and

.

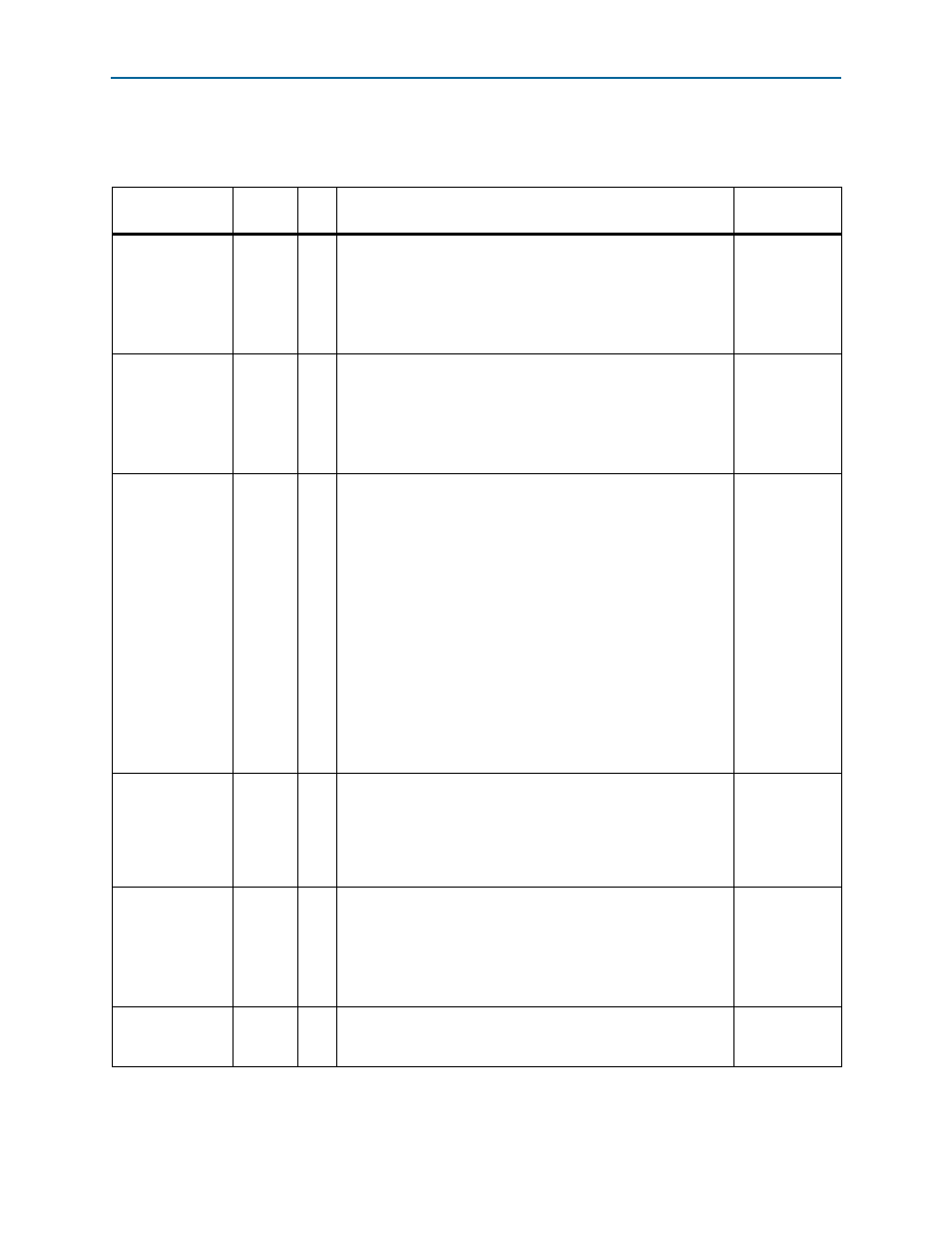

Table 5–15. Configuration Space Register Descriptions (Part 1 of 3)

Register

Width

Dir

Description

Register

Reference

cfg_devcsr

cfg_dev2csr

32

O

cfg_devcsr[31:16]

is status and cfg_devcsr[15:0] is device

control for the PCI Express capability structure.

cft_dev2csr[31:16]

is status 2 and cfg_dev2csr[15:0] is

device control 2 for the PCI Express capability structure.

0x088 (Gen1)

0x0A8 (Gen2)

cfg_slotcsr

16

O

cfg_slotcsr[31:16]

is the slot control and

cfg_slotcsr[15:0]

is the slot status of the PCI Express

capability structure. This register is only available in root port

mode.

0x098 (Gen1)

0x098 (Gen2)

cfg_linkcsr

32

O

cfg_linkcsr[31:16]

is the primary link status and

cfg_linkcsr[15:0]

is the primary link control of the PCI

Express capability structure.

0x090 (Gen1)

0x090 (Gen2)

cfg_link2csr

cfg_link2csr[31:16]

is the secondary link status and

cfg_link2csr[15:0]

is the secondary link control of the PCI

Express capability structure which was added for Gen2.

When tl_cfg_addr=2, tl_cfg_ctl returns the primary and

secondary link control registers, {cfg_linkcsr[15:0],

cfg_lin2csr[15:0]}

, the primary link status register,

cfg_linkcsr[31:16]

, is available on tl_cfg_sts[46:31].

For Gen1 variants, the link bandwidth notification bit is always set

to 0. For Gen2 variants, this bit is set to 1.

0x0B0 (Gen2,

only)

cfg_prmcsr

16

O

Base/Primary control and status register for the PCI configuration

space.

0x004 (Type 0)

0x004 (Type 1)

cfg_rootcsr

8

O

Root control and status register of the PCI-Express capability. This

register is only available in root port mode.

0x0A0 (Gen1)

0x0A0 (Gen2)

cfg_seccsr

16

O

Secondary bus control and status register of the PCI-Express

capability. This register is only available in root port mode.

0x01C