Table 5–10, Table 5–11 – Altera IP Compiler for PCI Express User Manual

Page 114

5–28

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

shows the layout of the Configuration MSI Control Status Register.

.

outlines the use of the various fields of the Configuration MSI Control

Status Register.

app_int_sts

I

Controls legacy interrupts. Assertion of app_int_sts causes an Assert_INTA message

TLP to be generated and sent upstream. Deassertion of app_int_sts causes a

Deassert_INTA message TLP to be generated and sent upstream.

app_int_ack

O

This signal is the acknowledge for app_int_sts. This signal is asserted for at least one

cycle either when the Assert_INTA message TLP has been transmitted in response to the

assertion of the app_int_sts signal or when the Deassert_INTA message TLP has been

transmitted in response to the deassertion of the app_int_sts signal. It is included on the

Avalon-ST interface for the hard IP implementation and the ×1 and ×4 soft IP

implementation. Refer to

timing information.

Table 5–9. Interrupt Signals for Endpoints (Part 2 of 2)

Signal

I/O

Description

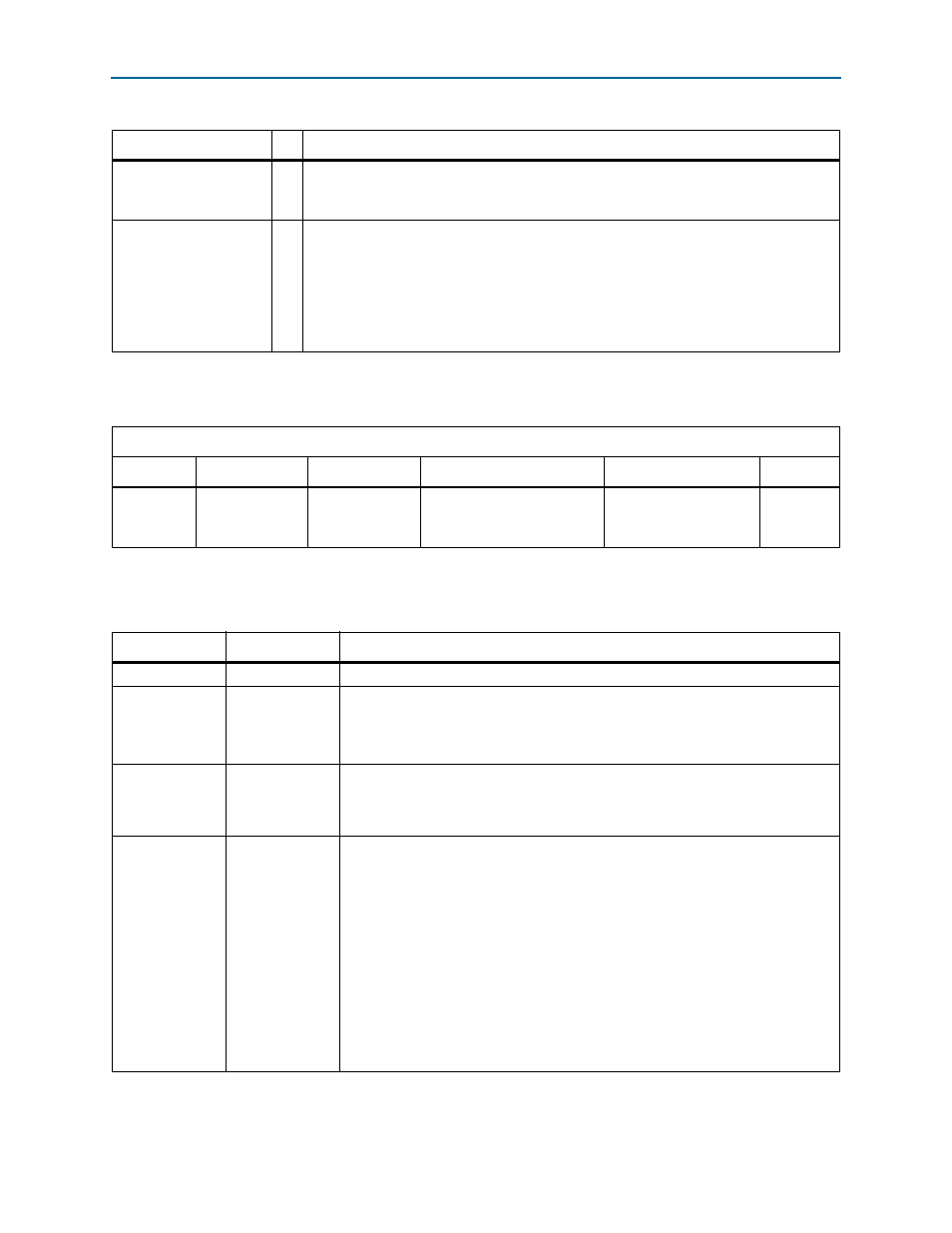

Table 5–10. Configuration MSI Control Status Register

Field and Bit Map

15

9

8

7

6

4

31

0

reserved

mask

capability

64-bit

address

capability

multiple message enable

multiple message

capable

MSI

enable

Table 5–11. Configuration MSI Control Status Register Field Descriptions (Part 1 of 2)

Bit(s)

Field

Description

[15:9]

Reserved

—

[8]

mask

capability

Per vector masking capable. This bit is hardwired to 0 because the IP core does not

support the optional MSI per vector masking using the Mask_Bits and

Pending_Bits

registers defined in

vector masking can be implemented using application layer registers.

[7]

64-bit

address

capability

64-bit address capable

■

1: IP core capable of sending a 64-bit message address

■

0: IP core not capable of sending a 64-bit message address

[6:4]

multiple

message

enable

Multiple message enable: This field indicates permitted values for MSI signals. For

example, if “100” is written to this field 16 MSI signals are allocated

■

000: 1 MSI allocated

■

001: 2 MSI allocated

■

010: 4 MSI allocated

■

011: 8 MSI allocated

■

100: 16 MSI allocated

■

101: 32 MSI allocated

■

110: Reserved

■

111: Reserved