Altera IP Compiler for PCI Express User Manual

Page 314

A–2

Chapter :

TLP Packet Format without Data Payload

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

\

Byte 8

Address[31:2]

0 0

Byte 12

Reserved

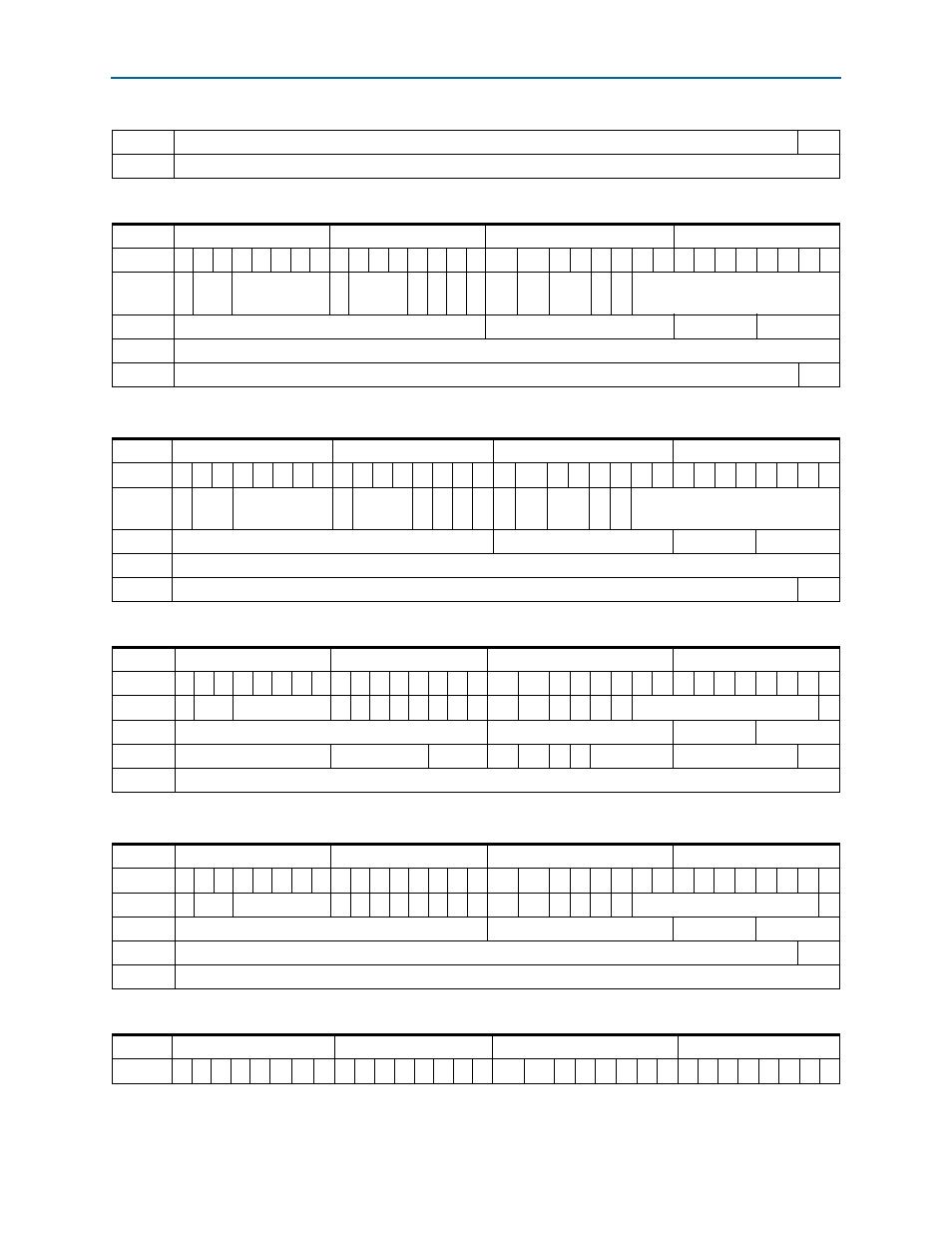

Table A–3. Memory Read Request, Locked 32-Bit Addressing

Table A–4. Memory Read Request, 64-Bit Addressing

+0

+1

+2

+3

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 0 1 0 0 0 0 0 0

TC

0 0 0 0

TD

EP

Att

r

0 0

Length

Byte 4

Requestor ID

Tag

Last BE

First BE

Byte 8

Address[63:32]

Byte 12

Address[31:2]

0 0

Table A–5. Memory Read Request, Locked 64-Bit Addressing

+0

+1

+2

+3

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 0 1 0 0 0 0 1 0

TC

0 0 0 0 T

EP

Att

r

0 0

Length

Byte 4

Requestor ID

Tag

Last BE

First BE

Byte 8

Address[63:32]

Byte 12

Address[31:2]

0 0

Table A–6. Configuration Read Request Root Port (Type 1)

+0

+1

+2

+3

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0

TD

EP

0 0 0 0 0 0 0 0 0 0 0 0 0 1

Byte 4

Requestor ID

Tag

0 0 0 0 First BE

Byte 8

Bus Number

Device No

Func

0

0

0 0

Ext Reg

Register No

0 0

Byte 12

Reserved

Table A–7. I/O Read Request

+0

+1

+2

+3

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

TD

EP

0 0 0 0 0 0 0 0 0 0 0 0 0 1

Byte 4

Requestor ID

Tag

0 0 0 0 First BE

Byte 8

Address[31:2]

0 0

Byte 12

Reserved

Table A–8. Message without Data

+0

+1

+2

+3

7 6 5 4 3 2

1

0

7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0