Power management signals – Altera IP Compiler for PCI Express User Manual

Page 125

Chapter 5: IP Core Interfaces

5–39

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

f

For a detailed description of the Avalon-MM protocol, refer to the Avalon

Memory-Mapped Interfaces chapter in the

.

Power Management Signals

shows the IP core’s power management signals. These signals are available

in configurations using the Avalon-ST interface or Descriptor/Data interface.

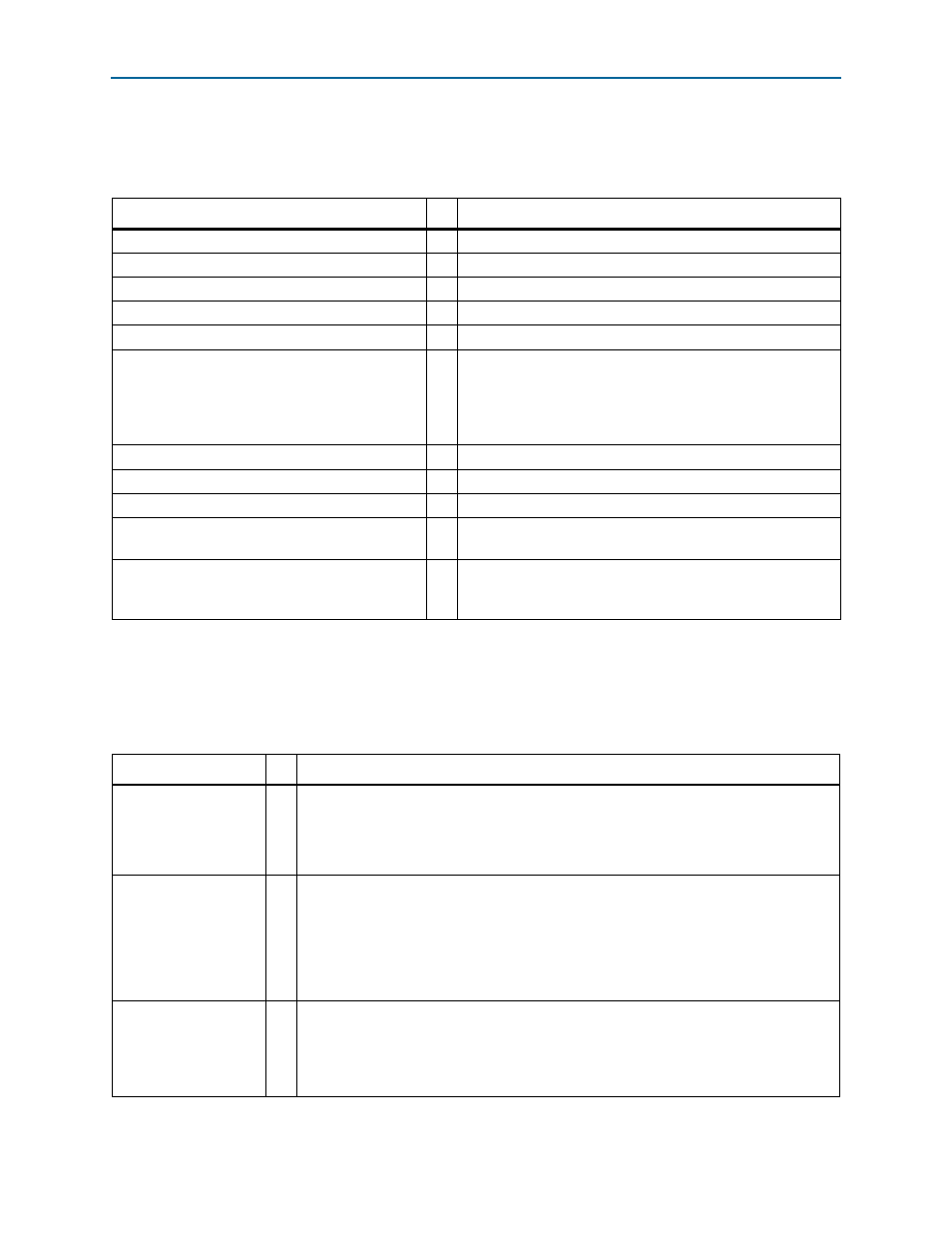

Table 5–18. Reconfiguration Block Signals (Hard IP Implementation)

Signal

I/O

Description

avs_pcie_reconfig_address[7:0]

I

A 8-bit address.

avs_pcie_reconfig_byteeenable[1:0]

I

Byte enables, currently unused.

avs_pcie_reconfig_chipselect

I

Chipselect.

avs_pcie_reconfig_write

I

Write signal.

avs_pcie_reconfig_writedata[15:0]

I

16-bit write data bus.

avs_pcie_reconfig_waitrequest

O

Asserted when unable to respond to a read or write request.

When asserted, the control signals to the slave remain constant.

waitrequest

can be asserted during idle cycles. An

Avalon-MM master may initiate a transaction when

waitrequest

is asserted.

avs_pcie_reconfig_read

I

Read signal.

avs_pcie_reconfig_readdata[15:0]

O

16-bit read data bus.

avs_pcie_reconfig_readdatavalid

O

Read data valid signal.

avs_pcie_reconfig_clk

I

Reconfiguration clock for the hard IP implementation. This

clock should not exceed 50MHz.

avs_pcie_reconfig_rstn

I

Active-low Avalon-MM reset. Resets all of the dynamic

reconfiguration registers to their default values as described in

.

Table 5–19. Power Management Signals

Signal

I/O

Description

pme_to_cr

I

Power management turn off control register.

Root port—When this signal is asserted, the root port sends the PME_turn_off message.

Endpoint—This signal is asserted to acknowledge the PME_turn_off message by sending

pme_to_ack

to the root port.

pme_to_sr

O

Power management turn off status register.

Root port—This signal is asserted for 1 clock cycle when the root port receives the

pme_turn_off

acknowledge message.

Endpoint—This signal is asserted when the endpoint receives the PME_turn_off message

from the root port. For the soft IP implementation, it is asserted until pme_to_cr is

asserted. For the hard IP implementation, it is asserted for one cycle.

cfg_pmcsr[31:0]

O

Power management capabilities register. This register is read-only and provides information

related to power management for a specific function. Refer to

for additional

information. This signal only exists in soft IP implementation. In the hard IP

implementation, this information is accessed through the configuration interface. Refer to

“Configuration Space Signals—Hard IP Implementation” on page 5–29

.