Altera IP Compiler for PCI Express User Manual

Page 255

Chapter 15: Testbench and Design Example

15–23

Root Port Design Example

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

■

Test Driver (altpcietb_bfm_driver_rp.v)—the chaining DMA endpoint test driver

which configures the root port and endpoint for DMA transfer and checks for the

successful transfer of data. Refer to the

“Test Driver Module” on page 15–18

for a

detailed description.

You can use the example root port design for Verilog HDL simulation. All of the

modules necessary to implement the example design with the variation file are

contained in

Compiler for PCI Express variation is generated.

The parameter editor creates the variation files in the top-level directory of your

project, including the following files:

■

The file instantiates the SERDES and PIPE interfaces, and the parameterized core,

■

■

■

The following modules are generated for the design example in the subdirectory

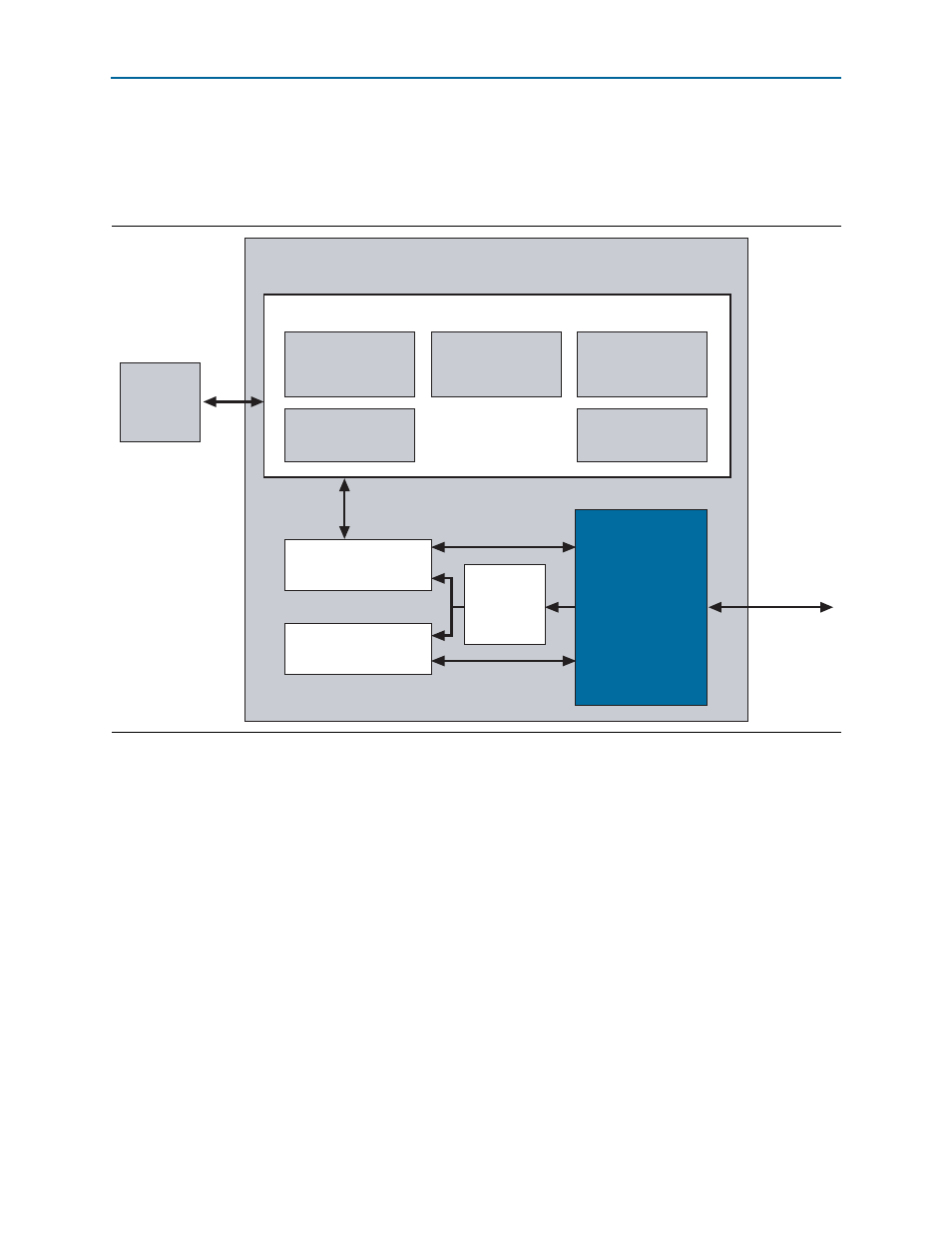

Figure 15–5. Root Port Design Example

IP Compiler

for PCI Express

Root Port

Variation

(variation_name.v)

VC1 Avalon-ST Interface

(altpcietb_bfm_vcintf_ast)

Config Bus

(altpcietb_tl_

cfg_sample.v)

Test Driver

(altpcietb_bfm_

driver_rp.v)

_example_rp_pipen1b.v

VC0 Avalon-ST Interface

(altpcietb_bfm_vcintf_ast)

BFM Shared Memory

(altpcietb_bfm_shmem)

BFM Read/Write Shared

Request Procedures

(altpcietb_bfm_rdwr)

BFM Configuration

Procedures

(altpcietb_bfm_configure)

BFM Request Interface

(altpcietb_bfm_req_intf)

BFM Log Interface

(altpcietb_bfm_log)

PCI Express

Root Port BFM Tasks and Shared Memory

Avalon-ST

Avalon-ST