Altera IP Compiler for PCI Express User Manual

Page 91

Chapter 5: IP Core Interfaces

5–5

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

lists the interfaces of both the hard IP and soft IP implementations with

links to the subsequent sections that describe each interface.

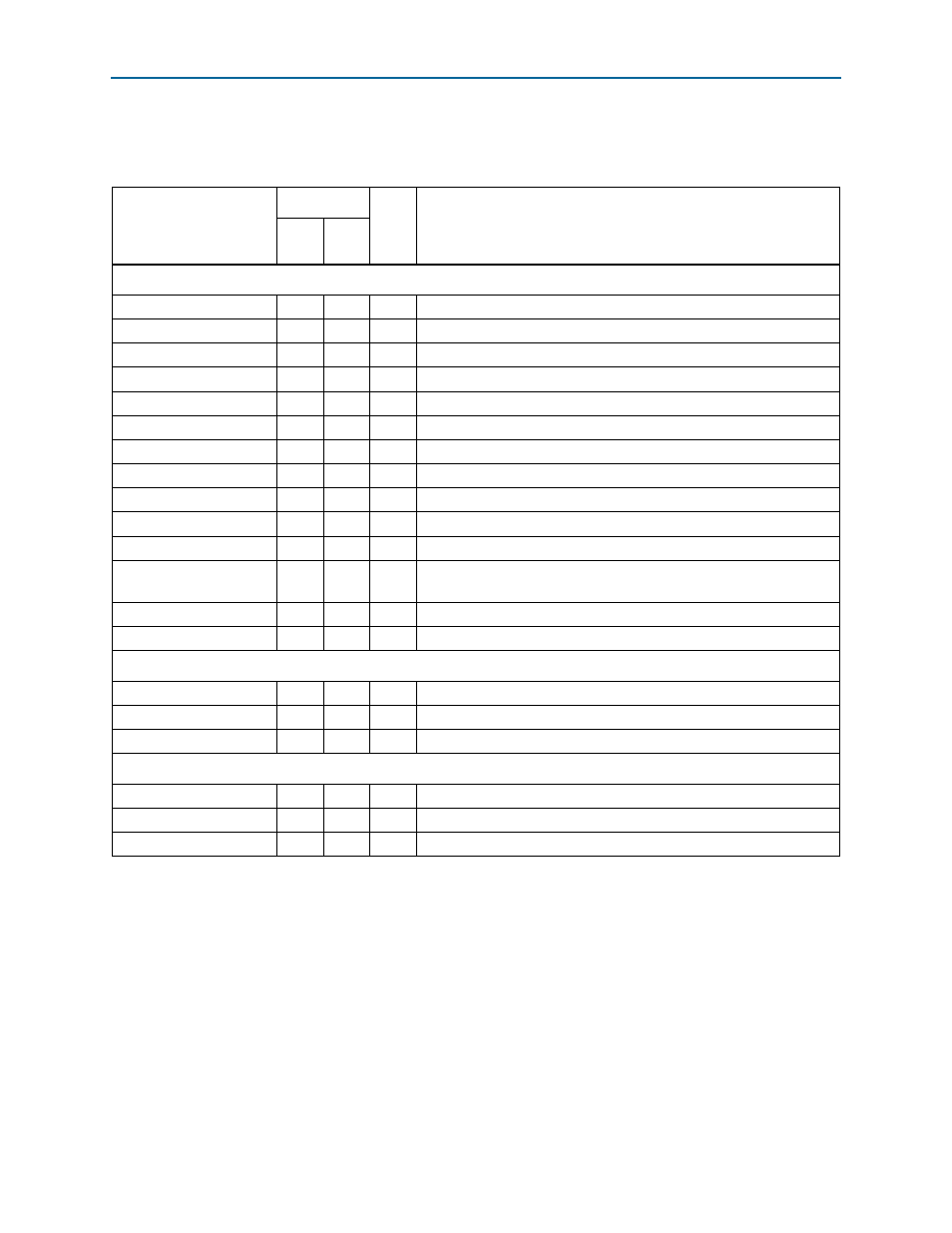

Table 5–1. Signal Groups in the IP Compiler for PCI Express with Avalon-ST Interface

Signal Group

Hard IP

Soft

IP

Description

End

point

Root

Port

Logical

Avalon-ST RX

v

v

v

“64- or 128-Bit Avalon-ST RX Port” on page 5–6

Avalon-ST TX

v

v

v

“64- or 128-Bit Avalon-ST TX Port” on page 5–15

Clock

v

v

—

“Clock Signals—Hard IP Implementation” on page 5–23

Clock

—

—

v

“Clock Signals—Soft IP Implementation” on page 5–23

Reset and link training

v

v

v

“Reset and Link Training Signals” on page 5–24

ECC error

v

v

—

“ECC Error Signals” on page 27

Interrupt

v

—

v

“PCI Express Interrupts for Endpoints” on page 5–27

Interrupt and global error

—

v

—

“PCI Express Interrupts for Root Ports” on page 5–29

Configuration space

v

v

—

“Configuration Space Signals—Hard IP Implementation” on page 5–29

Configuration space

—

—

v

“Configuration Space Signals—Soft IP Implementation” on page 5–36

LMI

v

v

—

“LMI Signals—Hard IP Implementation” on page 5–37

PCI Express

reconfiguration block

v

v

—

“IP Core Reconfiguration Block Signals—Hard IP Implementation” on

page 5–38

Power management

v

v

v

“Power Management Signals” on page 5–39

Completion

v

v

v

“Completion Side Band Signals” on page 5–41

Physical

Transceiver control

v

v

v

“Transceiver Control Signals” on page 5–53

Serial

v

v

v

“Serial Interface Signals” on page 5–55

PIPE

v

“PIPE Interface Signals” on page 5–56

Test

Test

v

v

“Test Interface Signals—Hard IP Implementation” on page 5–59

Test

—

—

v

“Test Interface Signals—Soft IP Implementation” on page 5–61

Test

v

v

v

Note to

(1) Provided for simulation only