Implementation. refer to, Figure 5–24 – Altera IP Compiler for PCI Express User Manual

Page 107

Chapter 5: IP Core Interfaces

5–21

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

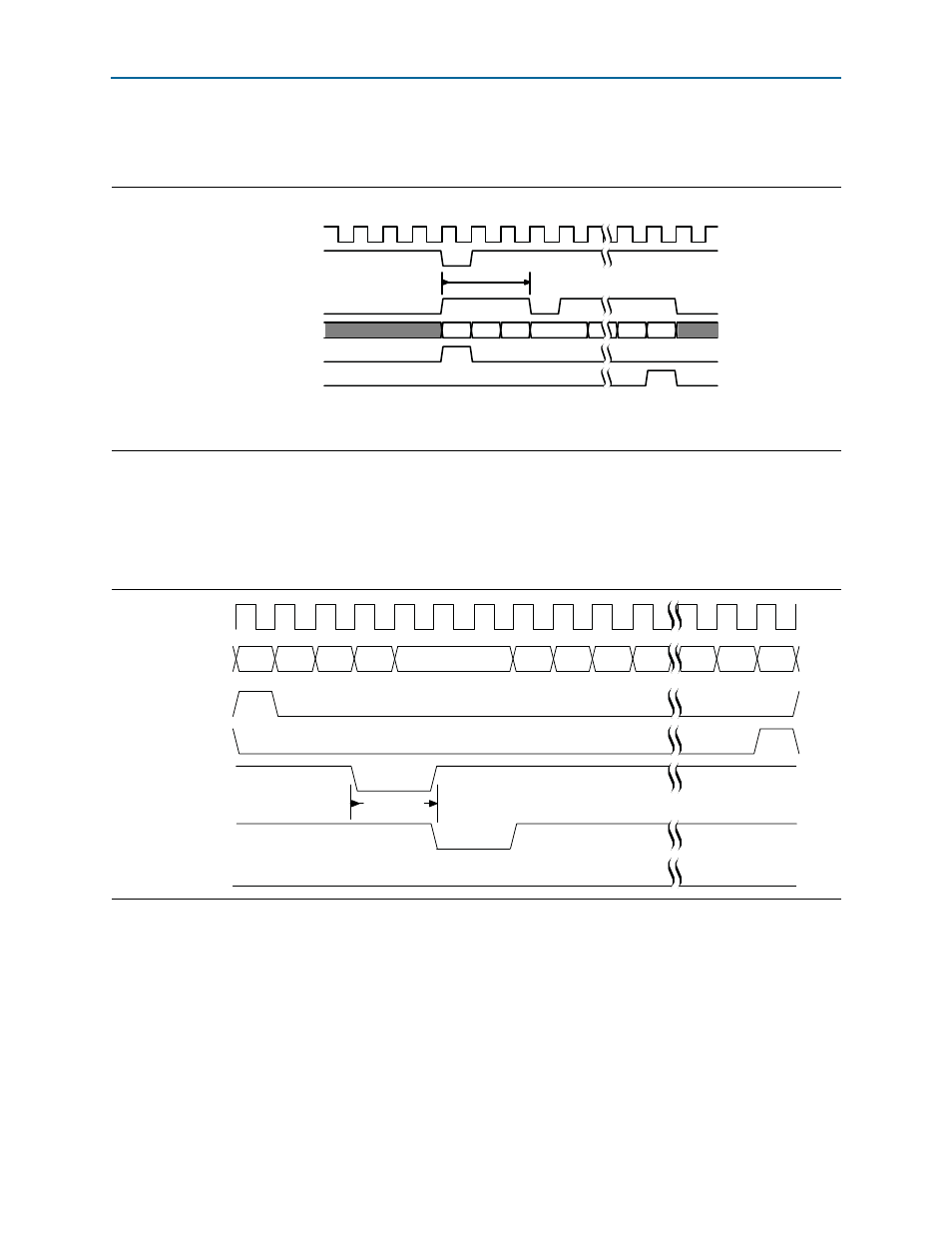

illustrates the timing of the Avalon-ST TX interface. The core can deassert

tx_st_ready

to throttle the application which is the source.

illustrates the timing of the 64-bit TX interface when the IP Compiler for

PCI Express backpressures the application by deasserting tx_st_ready. Because the

readyLatency

is two cycles, the application deasserts tx_st_valid after two cycles

and holds tx_st_data until two cycles after tx_st_ready is asserted.

Figure 5–24. Avalon-ST TX Interface Timing

Notes to

:

(1) The maximum allowed response time is 3 clock cycles for the soft IP implementation and 2 clock cycles for the hard IP implementation.

clk

tx_st_ready

tx_st_valid

tx_st_data0[63:0]

tx_st_sop

tx_st_eop

response_time

cycle 1 cycle 2 cycle 3

cycle 4

cycle n

. . .

1

2

3

4

5

6

7

8

9

10

11

12

13

Figure 5–25. 64-Bit Transaction Layer Backpressures the Application

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_err

tx_st_data[63:0]..

.

.

.

.

.

.

.

.

.

.

readyLatency

00. . 00 ... BB... BB ... BBBB0306BBB0305 BB...

BB..

BB ... BB ...

BB ... BB ... BB....