Table 5–31 – Altera IP Compiler for PCI Express User Manual

Page 143

Chapter 5: IP Core Interfaces

5–57

Physical Layer Interface Signals

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

for simulation of the PIPE interface for variations using an internal transceiver. In

, signals that include lane number 0 also exist for lanes 1-7, as marked in the

table. Refer to

for descriptions of the slightly modified

PIPE interface signalling for use with specific external PHYs. The modifications

include DDR signalling and source synchronous clocking in the TX direction.

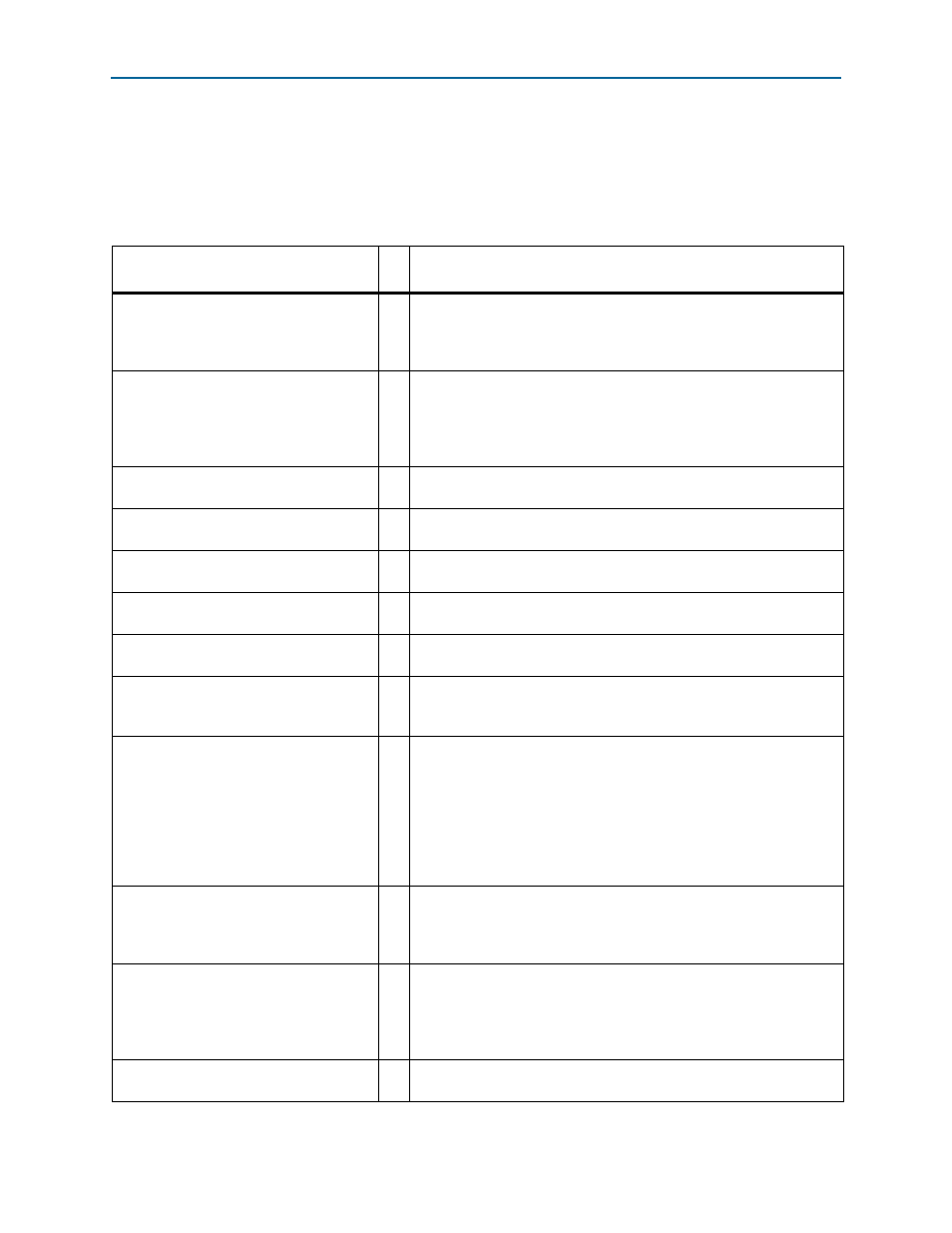

Table 5–31. PIPE Interface Signals (Part 1 of 2)

Signal Name in

Qsys

I/O

Description

txdata

pipe_ext_txdata0_ext[15:0]

O

Transmit data

lane

second transmitted symbol is txdata0_ext[15:8]. For the 8-bit PIPE

mode only txdata

txdatak

pipe_ext_txdatak

O

Transmit data control

as the control bit for txdata

first transmitted symbol and txdatak

(8B/10B encoding). For 8-bit PIPE mode only the single bit signal

txdatak

_ext is available.

txdetectrx

pipe_ext_txdetectrx

O

Transmit detect receive

receive detection operation or to begin loopback.

txelecidle

pipe_ext_txelecidle

O

Transmit electrical idle

electrical idle.

txcompl

pipe_ext_txcompl

O

Transmit compliance

negative in compliance mode (negative COM character).

rxpolarity

pipe_ext_rxpolarity

O

Receive polarity

inversion on the 8B/10B receiver decoding block.

powerdown

pipe_ext_powerdown

O

Power down

to the specified state (P0, P0s, P1, or P2).

tx_pipemargin/

internal signal in Qsys

O

Transmit V

OD

margin selection. The IP Compiler for PCI Express hard IP

sets the value for this signal based on the value from the Link Control 2

Register. Available for simulation only.

tx_pipedeemph/internal signal in

Qsys

O

Transmit de-emphasis selection. In PCI Express Gen2 (5 Gbps) mode it

selects the transmitter de-emphasis:

■

1'b0: -6 dB

■

1'b1: -3.5 dB

The PCI Express IP core hard IP sets the value for this signal based on

the indication received from the other end of the link during the Training

Sequences (TS). You do not need to change this value.

rxdata

pipe_ext_rxdata

I

Receive data

lane

second is rxdata

rxdata

is available.

rxdatak

pipe_ext_rxdatak

I

Receive data control

control and data symbols. The first symbol received is aligned with

rxdatak

and the second symbol received is aligned with

rxdata

. For the 8 Bit PIPE mode only the single bit signal

rxdatak

is available.

rxvalid

I

Receive valid

rxdata

and rxdatak