Test interface signals—hard ip implementation, For m, Table 5–33 – Altera IP Compiler for PCI Express User Manual

Page 145

Chapter 5: IP Core Interfaces

5–59

Test Signals

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

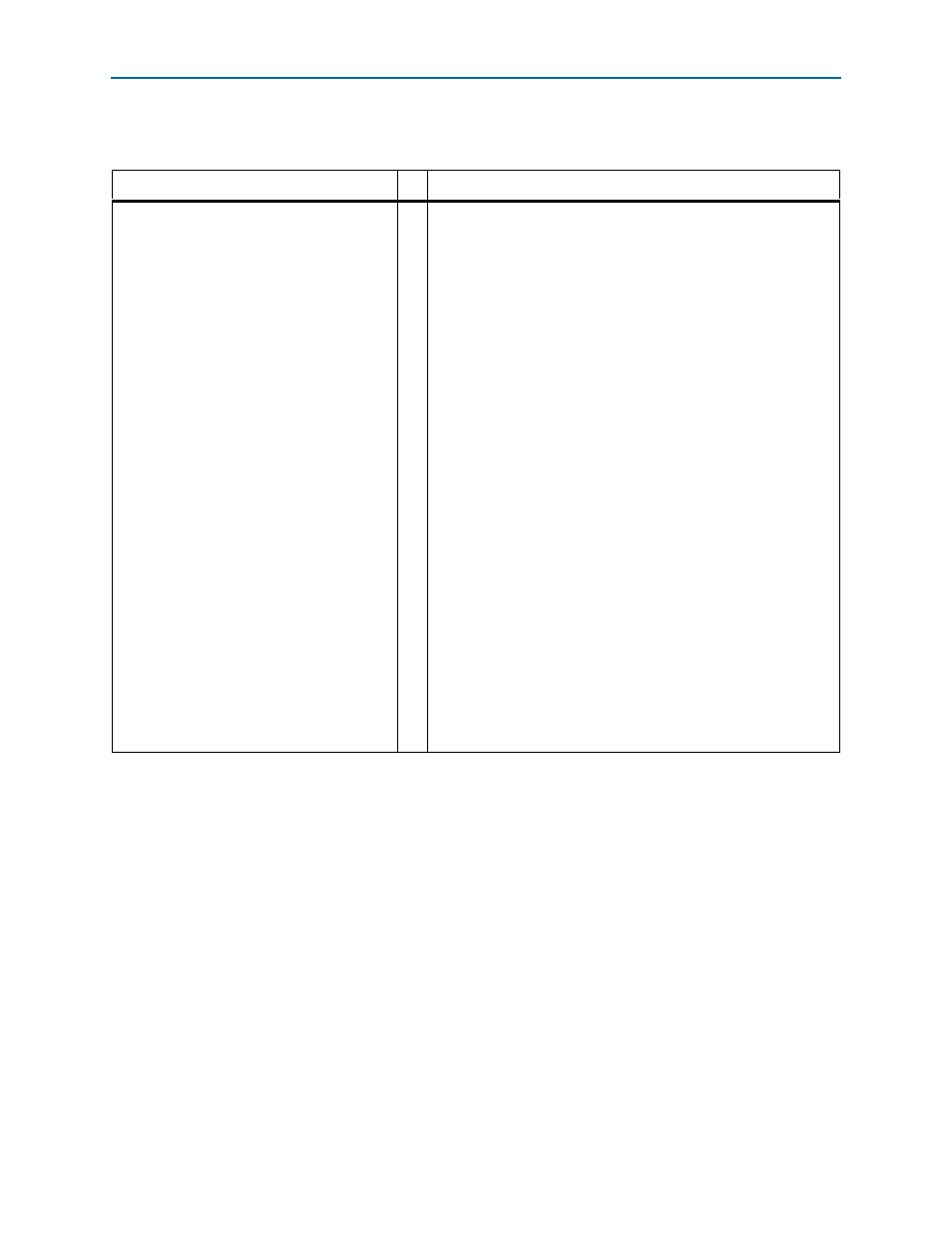

Test Interface Signals—Hard IP Implementation

Table 5–33. Test Interface Signals—Hard IP Implementation (Part 1 of 2)

Signal

I/O

Description

test_in[39:0]

(hard IP)

I

The test_in bus provides runtime control for specific IP core

features. For normal operation, this bus can be driven to all 0's. The

following bits are defined:

[0]–Simulation mode. This signal can be set to 1 to accelerate

initialization by changing many initialization count.

[2:1]–reserved.

[3]–FPGA mode. Set this signal to 1 for an FPGA implementation.

[2:1]–reserved.

[6:5] Compliance test mode. Disable/force compliance mode:

■

bit 0–when set, prevents the LTSSM from entering compliance

mode. Toggling this bit controls the entry and exit from the

compliance state, enabling the transmission of Gen1 and Gen2

compliance patterns.

■

bit 1–forces compliance mode. Forces entry to compliance mode

when timeout is reached in polling.active state (and not all lanes

have detected their exit condition).

[7]–Disables low power state negotiation. When asserted, this signal

disables all low power state negotiation. This bit is set to 1 for Qsys.

[11:8]–you must tie these signals low.

[15:13]–lane select.

[31:16, 12]–reserved.

[32] Compliance mode test switch. When set to 1, the IP core is in

compliance mode which is used for Compliance Base Board testing

(CBB) testing. When set to 0, the IP core is in operates normally.

Connect this signal to a switch to turn on and off compliance mode.

Refer to th

for an

actual coding example to specify CBB tests.