Altera IP Compiler for PCI Express User Manual

Page 158

6–10

Chapter 6: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Content

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Each entry in the PCI Express address translation table (

) is 8 bytes wide,

regardless of the value in the current PCI Express address width parameter. Therefore,

register addresses are always the same width, regardless of IP Compiler for PCI

Express address width.

The format of the address space field (A2P_ADDR_SPACEn) of the address

translation table entries is shown in

.

PCI Express to Avalon-MM Interrupt Status and Enable Registers

The registers in this section contain status of various signals in the PCI Express

Avalon-MM bridge logic and allow Avalon interrupts to be asserted when enabled. A

processor local to the system interconnect fabric that processes the Avalon-MM

interrupts can access these registers. These registers must not be accessed by the PCI

Express Avalon-MM bridge master ports; however, there is nothing in the hardware

that prevents this.

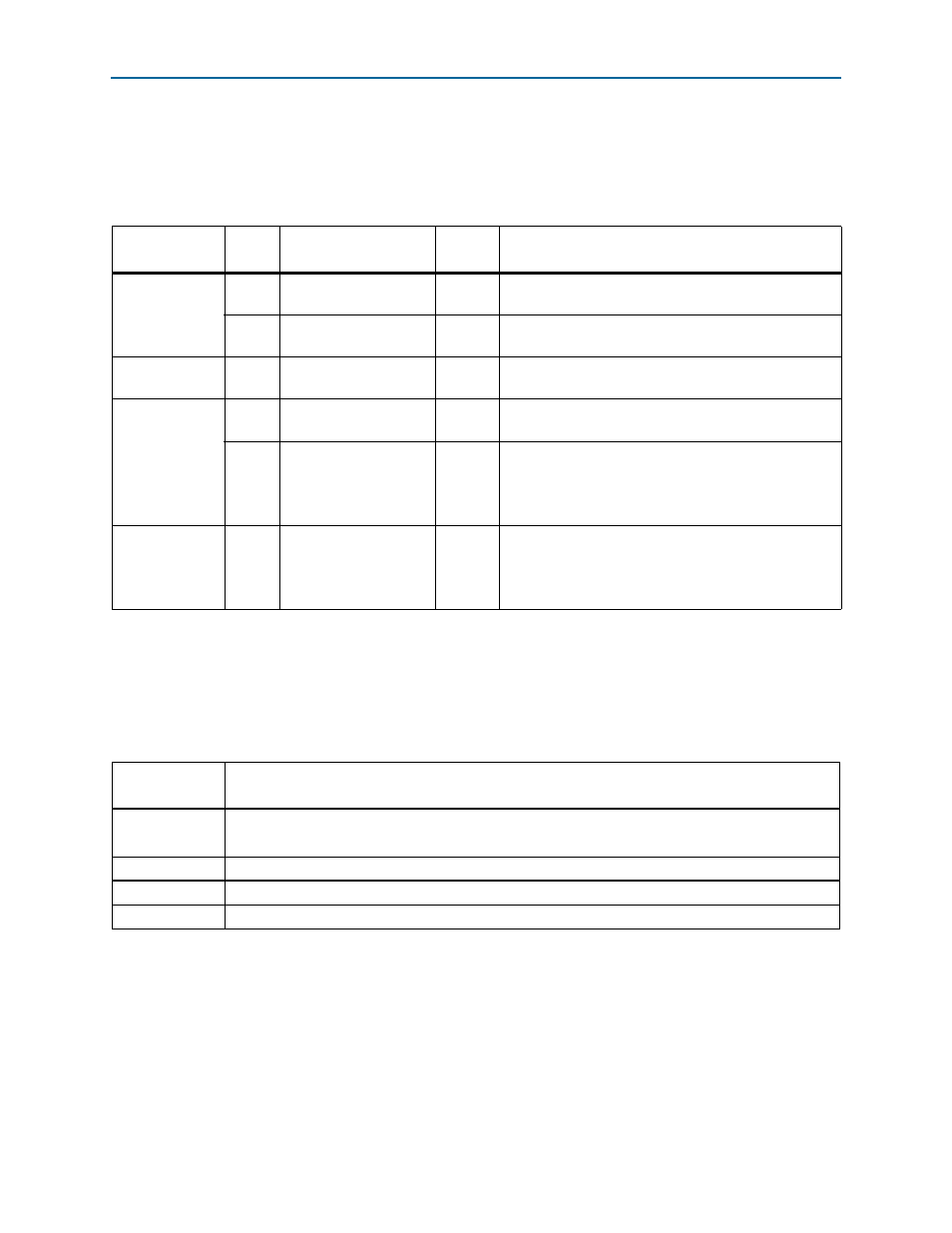

Table 6–17. Avalon-MM-to-PCI Express Address Translation Table

Address Range: 0x1000-0x1FFF

Address

Bits

Name

Access

Description

0x1000

[1:0]

A2P_ADDR_SPACE0

RW

Address space indication for entry 0. Refer to

for the definition of these bits.

[31:2]

A2P_ADDR_MAP_LO0

RW

Lower bits of Avalon-MM-to-PCI Express address map

entry 0.

0x1004

[31:0]

A2P_ADDR_MAP_HI0

RW

Upper bits of Avalon-MM-to-PCI Express address map

entry 0.

0x1008

[1:0]

A2P_ADDR_SPACE1

RW

Address space indication for entry 1. Refer to

for the definition of these bits.

[31:2]

A2P_ADDR_MAP_LO1

RW

Lower bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if number of table entries

is greater than 1.

0x100C

[31:0]

A2P_ADDR_MAP_HI1

RW

Upper bits of Avalon-MM-to-PCI Express address map

entry 1.

This entry is only implemented if the number of table

entries is greater than 1.

Note to

:

(1) These table entries are repeated for each address specified in the Number of address pages parameter (

). If Number

of address pages is set to the maximum of 512, 0x1FF8 contains A2P_ADDR_MAP_LO511 and 0x1FFC contains A2P_ADDR_MAP_HI511.

Table 6–18. PCI Express Avalon-MM Bridge Address Space Bit Encodings

Value

(Bits 1:0)

Indication

00

Memory Space, 32-bit PCI Express address. 32-bit header is generated.

Address bits 63:32 of the translation table entries are ignored.

01

Memory space, 64-bit PCI Express address. 64-bit address header is generated.

10

Reserved

11

Reserved