Receive datapath interface signals – Altera IP Compiler for PCI Express User Manual

Page 321

Chapter :

B–3

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

In

, the transmit and receive signals apply to each implemented virtual

channel, while configuration and global signals are common to all virtual channels on

a link.

lists the interfaces for this IP Compiler for PCI Express with links to the

sections that describe each interface.

Receive Datapath Interface Signals

The receive interface, like the transmit interface, is based on two independent buses:

one for the descriptor phase (rx_desc[135:0]) and one for the data phase

(rx_data[63:0]). Every transaction includes a descriptor. A descriptor is a standard

transaction layer packet header as defined by

tions. Bits 126 and 127 indicate the transaction layer packet

group and bits 135:128 describe BAR and address decoding information. Refer to

rx_desc[135:0]

in

for details.

Receive datapath signals can be divided into the following two groups:

■

Descriptor phase signals

■

Data phase signals

1

In the following tables, transmit interface signal names with an

virtual channel

additional set of signals for each virtual channel number.

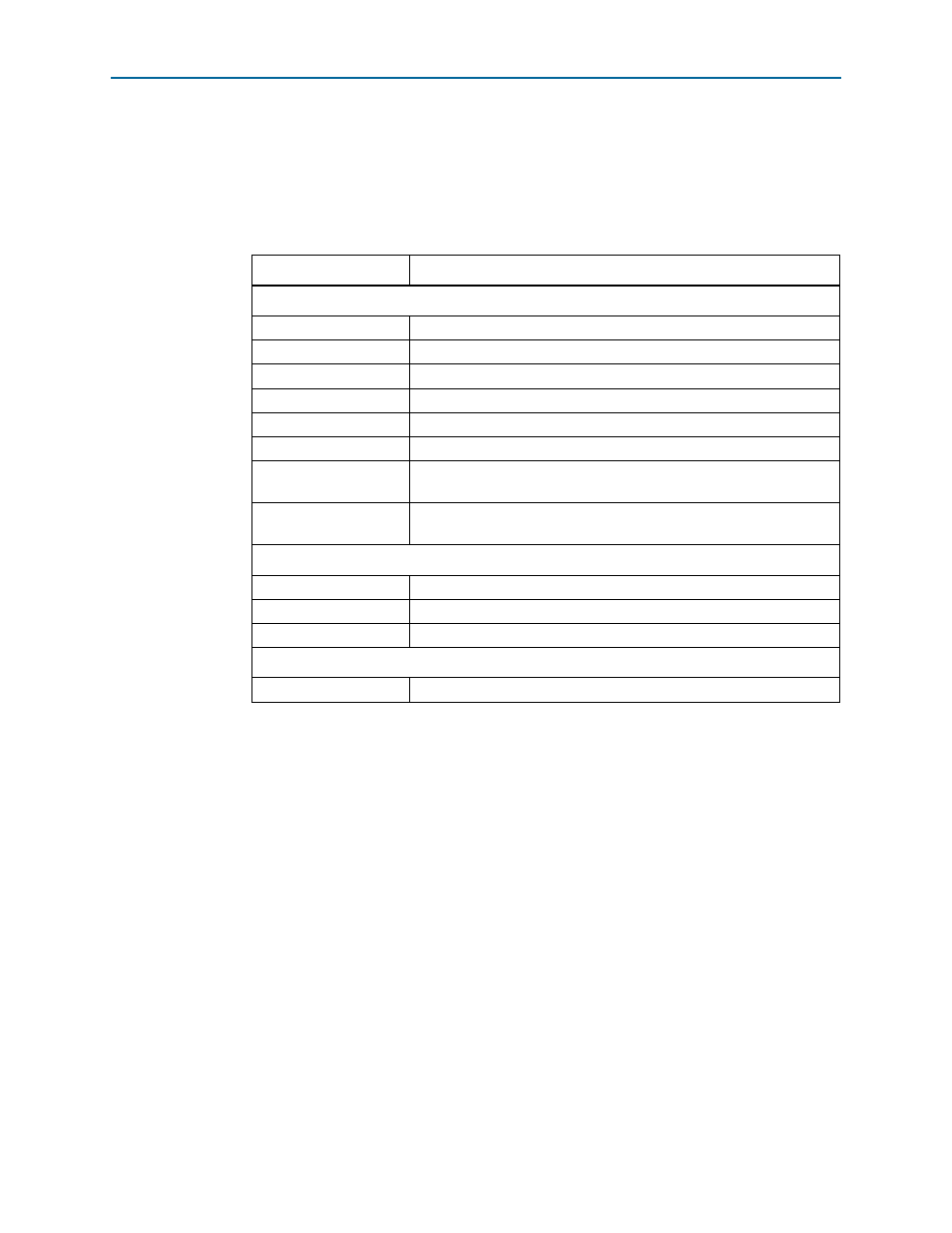

Table B–1. Signal Groups in the IP Compiler for PCI Express using the Descriptor/Data Interface

Signal Group

Description

Logical

Descriptor RX

“Receive Datapath Interface Signals” on page B–3

Descriptor TX

“Transmit Operation Interface Signals” on page B–12

Clock

“Clock Signals—Soft IP Implementation” on page 5–23

Reset

“Reset and Link Training Signals” on page 5–24

Interrupt

“PCI Express Interrupts for Endpoints” on page 5–27

Configuration space

“Configuration Space Signals—Soft IP Implementation” on page 5–36

Power management

“IP Core Reconfiguration Block Signals—Hard IP Implementation” on

page 5–38

Completion

“Completion Interface Signals for Descriptor/Data Interface” on

page B–25

Physical

Transceiver Control

“Transceiver Control Signals” on page 5–53

Serial

“Serial Interface Signals” on page 5–55

Pipe

“PIPE Interface Signals” on page 5–56

Test

Test

“Test Interface Signals—Soft IP Implementation” on page 5–61