Stratix iii family, Stratix iv family – Altera IP Compiler for PCI Express User Manual

Page 360

C–6

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

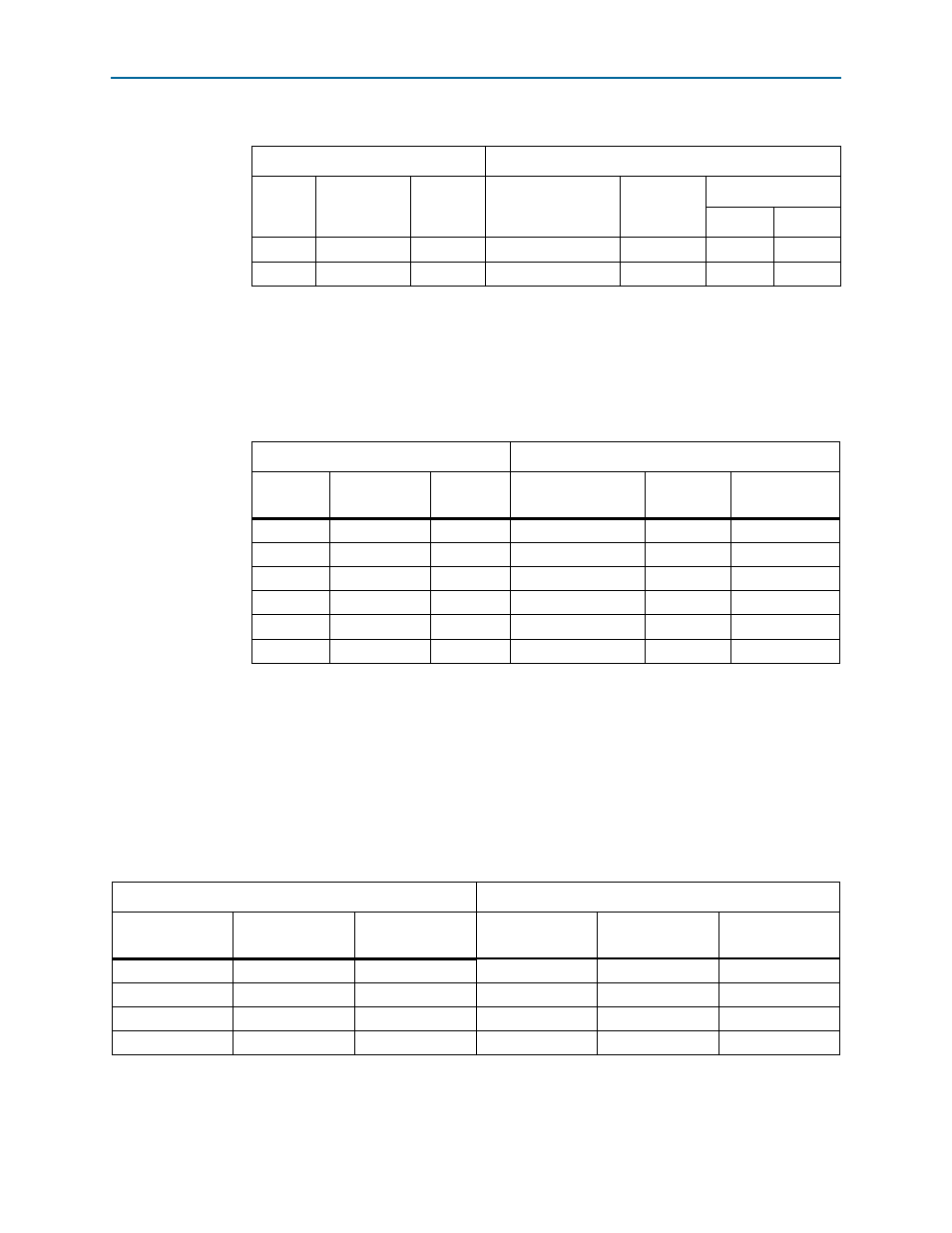

Stratix III Family

shows the typical expected performance and resource utilization of

Stratix III (EP3SL200F1152C2) devices for a maximum payload of 256 bytes with

different parameters, using the Quartus II software, version 11.0.

Stratix IV Family

shows the typical expected performance and resource utilization of

Stratix IV (EP4SGX290FH29C2X) devices for a maximum payload of 256 bytes with

different parameters, using the Quartus II software, version 11.0.

×8

250

1

6200

5600

10

16

×8

250

2

6900

6200

8

16

Table C–9. Performance and Resource Utilization, Descriptor/Data Interface - Stratix II and

Stratix II GX Devices (Part 2 of 2)

Parameters

Size

×1/ ×4

Internal

Clock (MHz)

Virtual

Channels

Combinational

ALUTs

Logic

Registers

Memory Blocks

M512

M4K

Table C–10. Performance and Resource Utilization, Descriptor/Data Interface - Stratix III Family

Parameters

Size

×1/ ×4

Internal

Clock (MHz)

Virtual

Channels

Combinational

ALUTs

Dedicated

Registers

M9K Memory

Blocks

×1

125

1

5100

3800

3

×1

125

2

6200

4600

7

62.5

1

5300

3900

8

62.5

2

6200

4800

7

×4

125

1

6700

4500

9

×4

125

2

7700

5300

12

Notes to

:

(1) C4 device used.

(2) C3 device used.

Table C–11. Performance and Resource Utilization, Descriptor/Data Interface - Stratix IV Family

Parameters

Size

×1/ ×4

Internal

Clock (MHz)

Virtual

Channels

Combinational

ALUTs

Dedicated

Registers

M9K Memory

Blocks

×1

125

1

5200

3600

5

×1

125

2

6200

4400

8

×4

125

1

6800

4600

7

×4

125

2

7900

5500

10