Uncorrectable and correctable error status bits – Altera IP Compiler for PCI Express User Manual

Page 208

12–6

Chapter 12: Error Handling

Uncorrectable and Correctable Error Status Bits

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Poisoned transaction layer packets can also set the parity error bits in the PCI

configuration space status register.

lists the conditions that cause parity

errors.

Poisoned packets received by the IP core are passed to the application layer. Poisoned

transmit transaction layer packets are similarly sent to the link.

Uncorrectable and Correctable Error Status Bits

The following section is reprinted with the permission of PCI-SIG. Copyright 2010

PCI-SIGR.

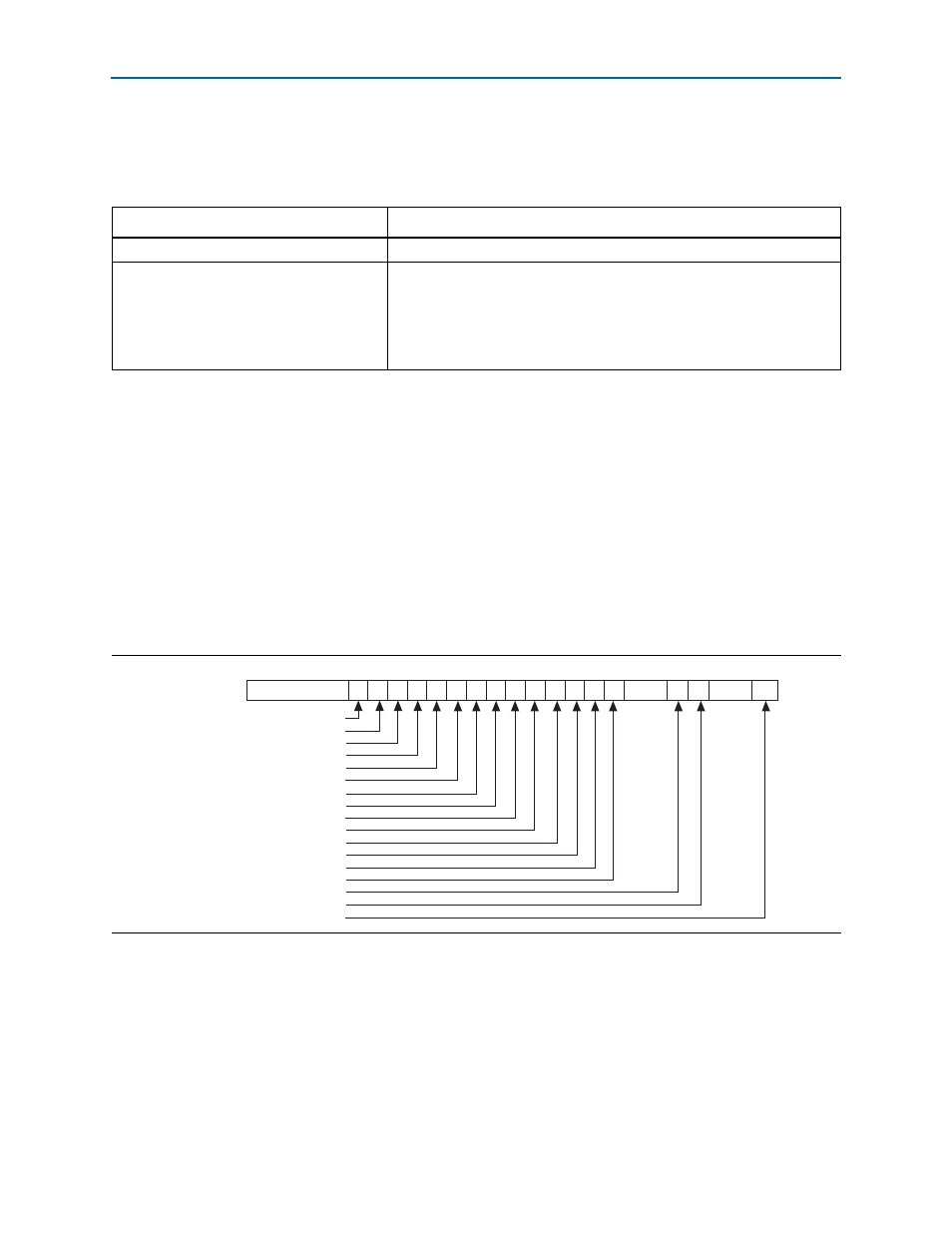

illustrates the Uncorrectable Error Status register. The default value of all

the bits of this register is 0. An error status bit that is set indicates that the error

condition it represents has been detected. Software may clear the error status by

writing a 1 to the appropriate bit.

Table 12–5. Parity Error Conditions

Status Bit

Conditions

Detected parity error (status register bit 15)

Set when any received transaction layer packet is poisoned.

Master data parity error (status register bit 8)

This bit is set when the command register parity enable bit is set and one of

the following conditions is true:

■

The poisoned bit is set during the transmission of a write request

transaction layer packet.

■

The poisoned bit is set on a received completion transaction layer packet.

Figure 12–1. Uncorrectable Error Status Register

Rsvd

Rsvd

Rsvd

TLP Prefix Blocked Error Status

AtomicOp Egress Blocked Status

MC Blocked TLP Status

Uncorrectable Internal Error Status

ACS Violation Status

Unsupported Request Error Status

ECRC Error Status

Malformed TLP Status

Receiver Overflow Status

Unexpected Completion Status

Completer Abort Status

Completion Timeout Status

Flow Control Protocol Status

Poisoned TLP Status

Surprise Down Error Status

Data Link Protocol Error Status

Undefined

22 21 20 19

26 25 24 23

18 17 16 15 14 13 12 11

6

5

4

3

1

0

31