Altera IP Compiler for PCI Express User Manual

Page 133

Chapter 5: IP Core Interfaces

5–47

Avalon-MM Application Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

shows the signals of a completer-only, single dword, IP Compiler for PCI

Express.

lists the interfaces for these IP cores with links to the sections that describe

them.

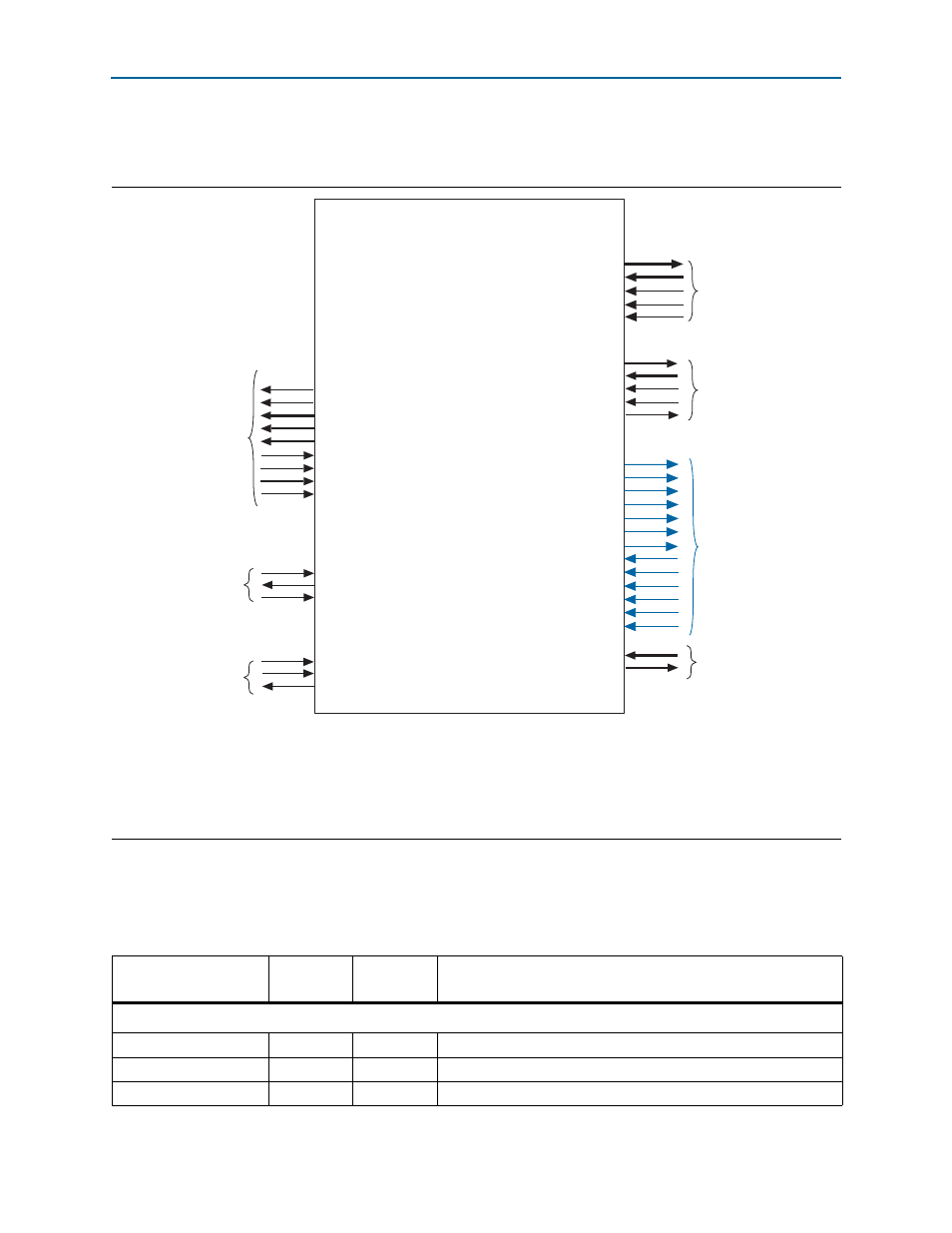

Figure 5–39. Signals in the Qsys Completer-Only, Single Dword, IP Core with Avalon-MM Interface

Notes to

:

(1) This variant is only available in the hard IP implementation.

(2) Signals in blue are for simulation only.

tx[3:0]

rx[3:0]

pipe_mode

xphy_pll_areset

xphy_pll_locked

txdatak0_ext

txdata0_ext[7:0]

txdetectrx_ext

txelectidle0_ext

rxpolarity0_ext

txcompl0_ext

powerdown0_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus_ext

rxelectidle0_ext

rxstatus0_ext[2:0]

1-Bit Serial

RxmIrq

Bar<a>_<b>_readdatavalid

Bar<a>_<b>_waitrequest

Bar<a>_<b>_address<n>[31:0]

Bar<a>_<b>_readdata_i[31:0]

Bar<a>_<b>_byteenable<n>[3:0]

Bar<a>_<b>_write<n>

Bar<a>_<b>_read<n>

Bar<a>_<b>_writedata<n>[31:0]

32-Bit

Avalon-MM Rx

Master Port

reset_n

Clock

Reset &

Status

clk125_out

fixedclk_serdes

refclk

pcie_rstn

suc_spd_neg

Signals in the Completer Only Single Dword

IP Compiler for PCI Express (1)

(Qsys Generated)

Hard IP

Implementation

Simulation

Only

8-Bit PIPE

Test

Interface

test_out[511:0], [63:0], or [9:0]

test_in[31:0]

(test_out is optional)

reconfig_fromgxb[

reconfig_togxb[

reconfig_clk

cal_blk_clk

gxb_powerdown

Transceiver

Control

(2)

Table 5–22. Avalon-MM Signal Groups in the IP Compiler with PCI Express Variations with an Avalon-MM

Interface (Part 1 of 2)

Signal Group

Full

Featured

Completer

Only

Description

Logical

Avalon-MM CRA Slave

v

—

“32-Bit Non-Bursting Avalon-MM CRA Slave Signals” on page 5–48

Avalon-MM RX Master

v

v

“RX Avalon-MM Master Signals” on page 5–49

Avalon-MM TX Slave

v

—