Altera IP Compiler for PCI Express User Manual

Page 58

3–22

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

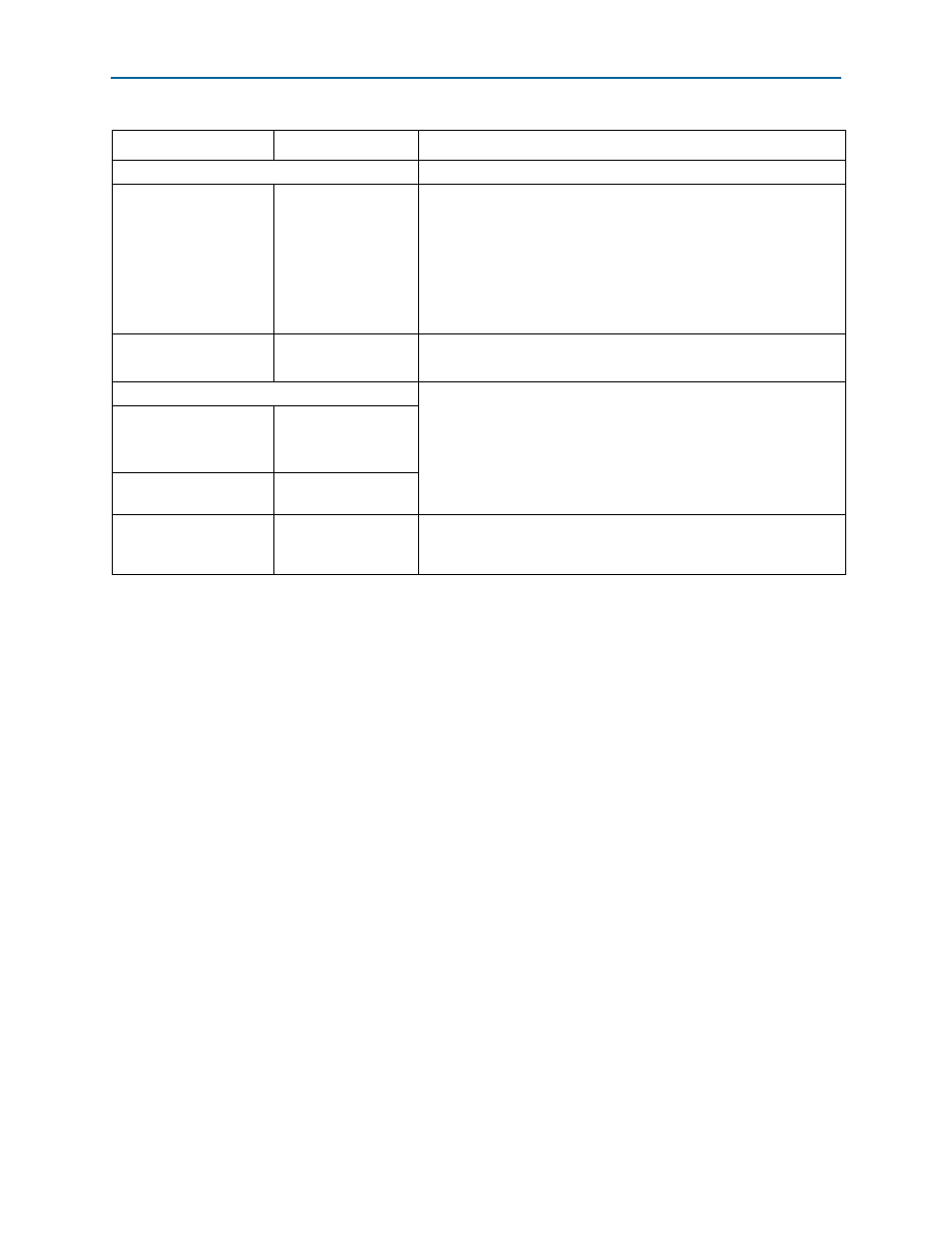

Address translation table size

Sets Avalon-MM-to-PCI Express address translation windows and size.

Number of address

pages

1, 2, 4, 8, 16, 32, 64,

128, 256, 512

Specifies the number of PCI Express base address pages of memory

that the bridge can access. This value corresponds to the number of

entries in the address translation table. The Avalon address range is

segmented into one or more equal-sized pages that are individually

mapped to PCI Express addresses. Select the number and size of the

address pages. If you select Dynamic translation table, use several

address translation table entries to avoid updating a table entry before

outstanding requests complete.

Size of address pages

1 MByte–2 GBytes

Specifies the size of each PCI Express memory segment accessible by

the bridge. This value is common for all address translation entries.

Fixed Address Translation Table Contents

Specifies the type and PCI Express base addresses of memory that the

bridge can access. The upper bits of the Avalon-MM address are

replaced with part of a specific entry. The MSBs of the Avalon-MM

address, used to index the table, select the entry to use for each

request. The values of the lower bits (as specified in the size of address

pages parameter) entered in this table are ignored. Those lower bits are

replaced by the lower bits of the incoming Avalon-MM addresses.

PCIe base address

32-bit

64-bit

Type

32-bit Memory

64-bit Memory

Avalon-MM CRA port

Enable/Disable

Allows read/write access to bridge registers from Avalon using a

specialized slave port. Disabling this option disallows read/write access

to bridge registers.

Table 3–14. Avalon Configuration Settings (Part 2 of 2)

Parameter Value

Description