Register descriptions, Configuration space register content, Common configuration space header – Altera IP Compiler for PCI Express User Manual

Page 149

August 2014

Altera Corporation

IP Compiler for PCI Express U

6. Register Descriptions

This chapter describes registers that you can access in the PCI Express configuration

space and the Avalon-MM bridge control registers. It includes the following sections:

■

Configuration Space Register Content

■

PCI Express Avalon-MM Bridge Control Register Content

■

Comprehensive Correspondence between Config Space Registers and PCIe Spec

Rev 2.0

Configuration Space Register Content

shows the common configuration space header. The following tables

provide more details.

f

For comprehensive information about these registers, refer to Chapter 7 of the

depending on the version you specify

on the System Setting page of the parameter editor.

1

To facilitate finding additional information about these IP Compiler for PCI Express

registers, the following tables provide the name of the corresponding section in the

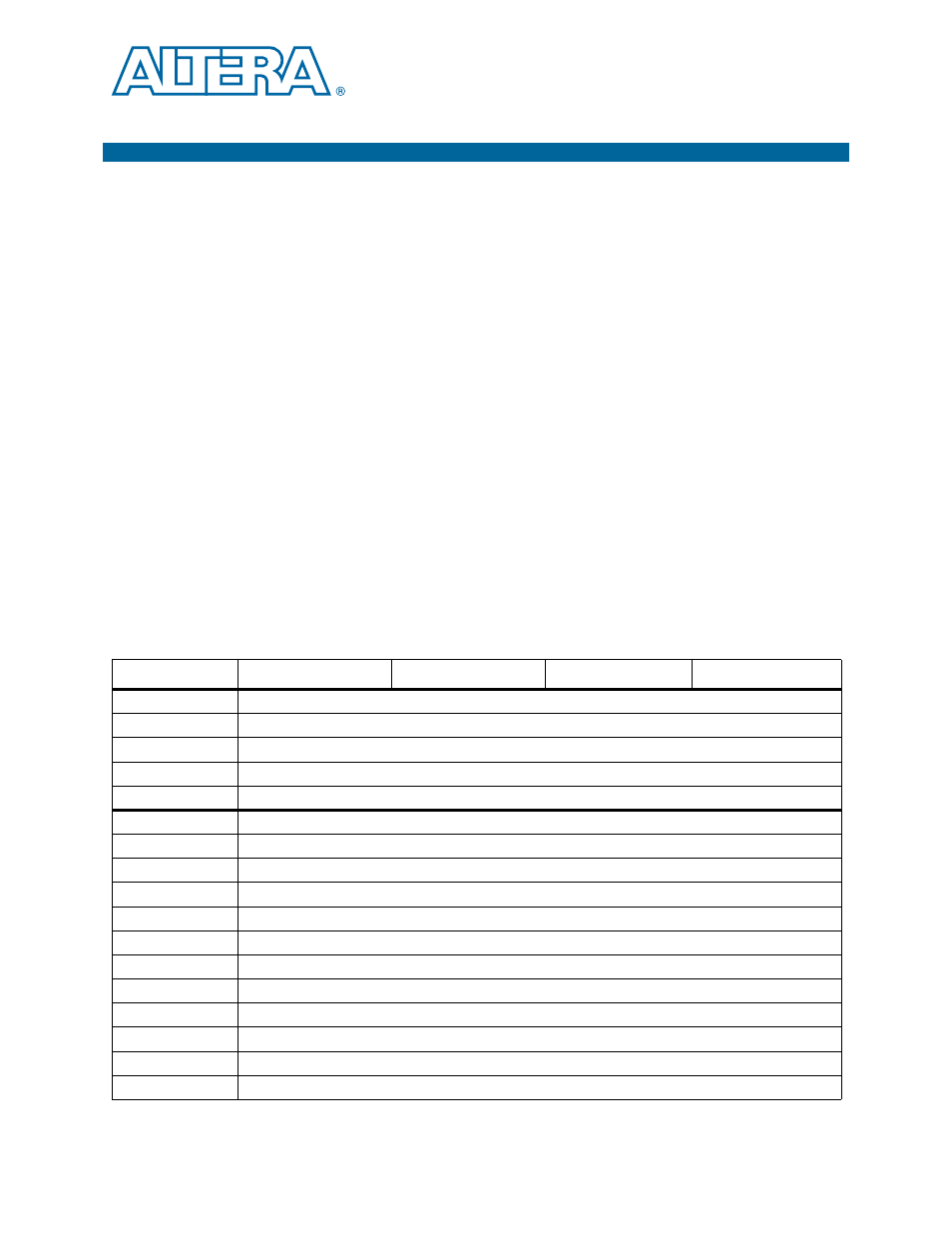

Table 6–1. Common Configuration Space Header (Part 1 of 2)

Byte Offset

31:24

23:16

15:8

7:0

0x000:0x03C

PCI Type 0 configuration space header (refer to

for details.)

0x000:0x03C

PCI Type 1 configuration space header (refer to

for details.)

0x040:0x04C

Reserved

0x050:0x05C

MSI capability structure, version 1.0a and 1.1 (refer to

for details.)

0x068:0x070

MSI–X capability structure, version 2.0 (refer to

for details.)

0x070:0x074

Reserved

0x078:0x07C

Power management capability structure (refer to

0x080:0x0B8

PCI Express capability structure (refer to

for details.)

0x080:0x0B8

PCI Express capability structure (refer to

for details.)

0x0B8:0x0FC

Reserved

0x094:0x0FF

Root port

0x100:0x16C

Virtual channel capability structure (refer to

for details.)

0x170:0x17C

Reserved

0x180:0x1FC

Virtual channel arbitration table

0x200:0x23C

Port VC0 arbitration table (Reserved)

0x240:0x27C

Port VC1 arbitration table (Reserved)

0x280:0x2BC

Port VC2 arbitration table (Reserved)

August 2014