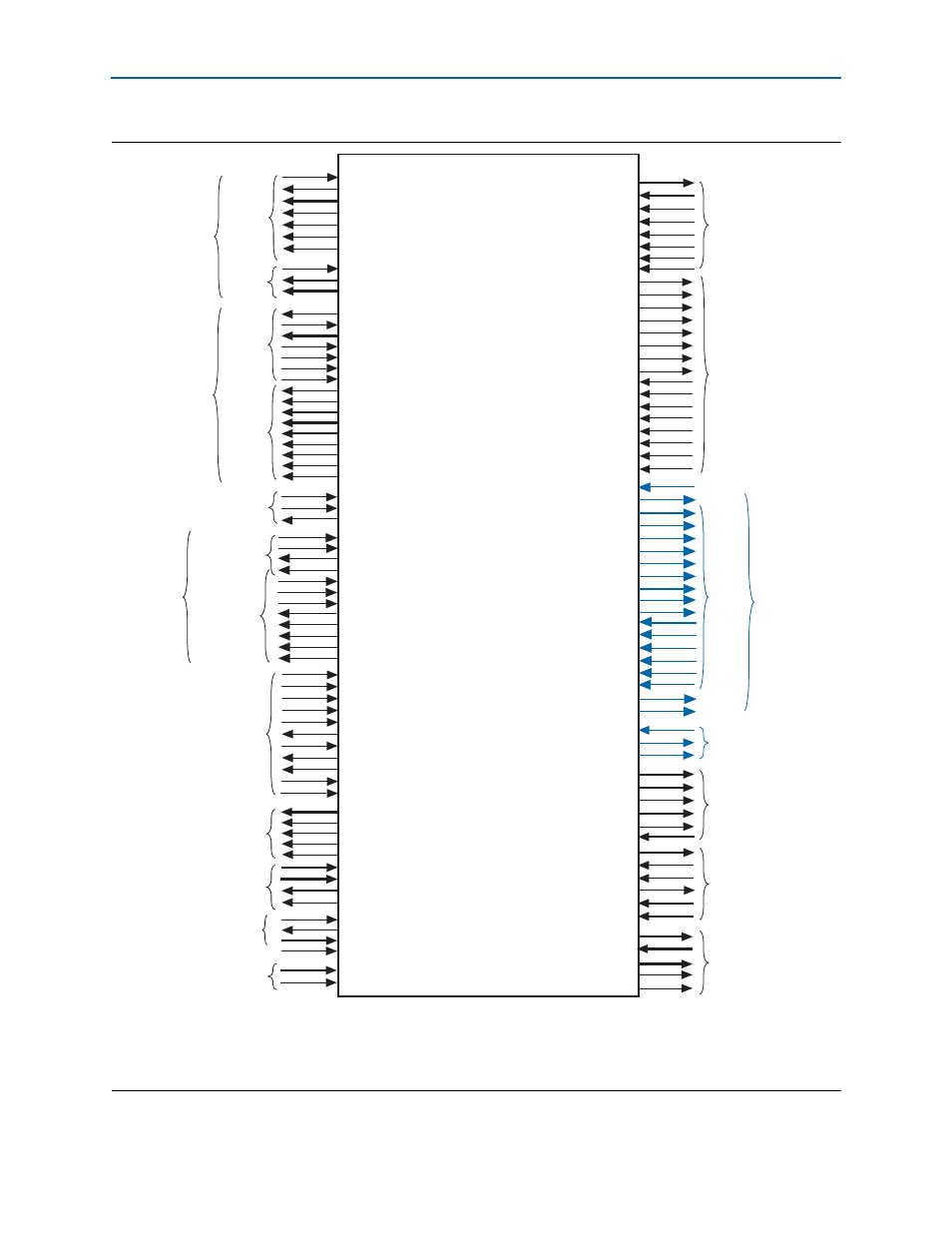

Figure 5–1 – Altera IP Compiler for PCI Express User Manual

Page 88

5–2

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

rx_st_ready0

rx_st_valid0

rx_st_data0[63..0], [127:0]

rx_st_sop0

rx_st_eop0

rx_st_empty

rx_st_err0

rx_st_mask0

rx_st_bardec0[7:0]

rx_st_be0[7:0], [15:0]

rx_fifo_full0

rx_fifo_empty0

Signals in the PCI Express Hard IP MegaCore Function

Test

Interface

Rx Port

(Path to

Virtual

Channel 0)

tx_st_ready0

tx_st_valid0

tx_st_data0[63..0], [127:0]

tx_st_sop0

tx_st_eop0

tx_st_empty

tx_st_err0

tx_fifo_full0

tx_fifo_empty0

tx_fifo_rdptr0[3:0]

tx_fifo_wrptr0[3:0]

tx_cred0[35..0]

refclk

pld_clk

core_clk_out

npor

srst

crst

l2_exit

hotrst_exit

dlup_exit

app_msi_req

app_msi_ack

app_msi_tc [2:0]

app_msi_num [4:0]

pex_msi_num [4:0]

app_int_sts

app_int_ack

pme_to_cr

pme_to_sr

cpl_err [6:0]

cpl_pending0

pclk_in

clk250_out

clk500_out

Interrupt

Reset

Clocks

Power

Mnmt

Completion

Interface

Clocks -

Simulation

Only (2)

Tx Port

(Path to

Virtual

Channel 0)

Config

LMI

(1)

(1)

(1)

lmi_dout[31:0]

lmi_ack

lmi_addr[11:0]

lmi_din[31:0]

lmi_rden

lmi_wren

pipe_mode

rate_ext

txdata0_ext[7:0]

txdatak0_ext

txdetectrx0_ext

txelecidle0_ext

txcompl0_ext

rxpolarity0_ext

powerdown0_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus0_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

8-bit

PIPE

Repeated for

Lanes 1-7

PIPE

Interface

Simulation

Only (2)

test_out[64:0]

test_in[15:0]

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

tl_cfg_ctl_wr

tl_cfg_sts[52:0]

tl_cfg_sts_wr

reconfig_fromgxb[1:0]

reconfig_clk

reconfig_togxb[2:0]

cal_blk_clk

Transceiver

Control

for

internal

PHY

tx_out0

tx_out1

tx_out2

tx_out3

tx_out4

tx_out5

tx_out6

tx_out7

rx_in0

rx_in1

rx_in2

rx_in3

rx_in4

rx_in5

rx_in6

rx_in7

Serial

IF to

PIPE

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

Figure 5–1. Signals in the Hard IP Implementation Root Port with Avalon-ST Interface Signals

Notes to

(1) Available in Arria II GX, Arria II GZ, Cyclone IV GX,, and Stratix IV G devices. TFor Stratix IV GX devices,

= 33 in the ×8 IP core.

(2) Available in Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX devices. For Stratix IV GX reconfig_togxb,

rx_st_ready

rx_st_sop

rx_st_mask

rx_st_be

avs_pcie_reconfig_address[7:0]

avs_pcie_reconfig_byteenable[1:0]

avs_pcie_reconfig_chipselect

avs_pcie_reconfig_write

avs_pcie_reconfig_writedata[15:0]

avs_pcie_reconfig_waitrequest

avs_pcie_reconfig_read

avs_pcie_reconfig_readdata[15:0]

avs_pcie_reconfig_readdatavalid

avs_pcie_reconfig_clk

avs_pcie_reconfig_rstn

IP Compiler for PCI Express Hard IP Implementation

Test

Interface

Rx Port

(Path to

Virtual

Channel

tx_st_ready

tx_st_sop

tx_fifo_wrptr

tx_cred

nph_alloc_1cred_vc0

npd_alloc_1cred_vc0

npd_cred_vio_vc0

nph_cred_vio_vc0

Clocks

Power

Mnmt

Completion

Interface

Clocks -

Simulation

Only

Tx Port

(Path to

Virtual

Channell

Reconfiguration

Block

(optional)

Config

ECC Error

Interrupts

LMI

(1)

(2)

lmi_dout[31:0]

lmi_ack

lmi_addr[11:0]

lmi_din[31:0]

lmi_rden

pclk_in

clk250_out

clk500_out

lmi_wren

pipe_mode

rate_ext

txdata0_ext[7:0]

txdatak0_ext

txdetectrx0_ext

txelecidle0_ext

txcompl0_ext

rxpolarity0_ext

powerdown0_ext[1:0]

tx_pipemargin

tx_pipedeemph

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus0_ext

rxelecidle0_ext

rxstatus0_ext[2:0]

pipe_rstn

pipe_txclk

8-bit

PIPE

PIPE

Interface

Simulation

Only

test_out[63:0]

test_in[39:0]

lane_act[3:0]

rx_st_fifo_full

rx_st_fifo_empty

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

tl_cfg_ctl_wr

tl_cfg_sts[52:0]

tl_cfg_sts_wr

hpg_ctrler[4:0]

reconfig_fromgxb[

reconfig_togxb[

reconfig_clk

cal_blk_clk

fixedclk_serdes

busy_altgxb_reconfig

reset_reconfig_altgxb_reconfig

gxb_powerdown

Transceiver

Control

These signals are

internal for

for

internal

PHY

tx_out0

tx_out1

tx_out2

tx_out3

tx_out4

tx_out5

tx_out6

tx_out7

rx_in0

rx_in1

rx_in2

rx_in3

rx_in4

rx_in5

rx_in6

rx_in7

Serial

IF to

PIPE

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

derr_cor_ext_rcv[1:0]

derr_rpl

derr_cor_ext_rpl

r2c_err0

r2c_err1

aer_msi_num[4:0]

pex_msi_num[4:0]

int_status[4:0]

serr_out

pme_to_cr

pme_to_sr

pm_data

pm_auxpwr

cpl_err[6:0]

cpl_pending

refclk

pld_clk

core_clk_out

pcie_rstn

local_rstn

suc_spd_neg

dl_ltssm[4:0]

npor

srst

crst

l2_exit

hotrst_exit

dlup_exit

reset_status

rc_pll_locked

Reset &

Link

Training