Altera IP Compiler for PCI Express User Manual

Page 8

1–6

Chapter 1: Datasheet

General Description

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

■

Physical Coding Sublayer (PCS)

■

Media Access Control (MAC)

■

Data link

■

Transaction

Optimized for Altera devices, the hard IP implementation supports all memory, I/O,

configuration, and message transactions. The IP cores have a highly optimized

application interface to achieve maximum effective throughput. Because the compiler

is parameterizeable, you can customize the IP cores to meet your design

requirements.

lists the configurations that are available for the IP Compiler

for PCI Express hard IP implementation.

lists the Total RX buffer space, Retry buffer size, and Maximum Payload

size

for device families that include the hard IP implementation. You can find these

parameters on the Buffer Setup page of the parameter editor.

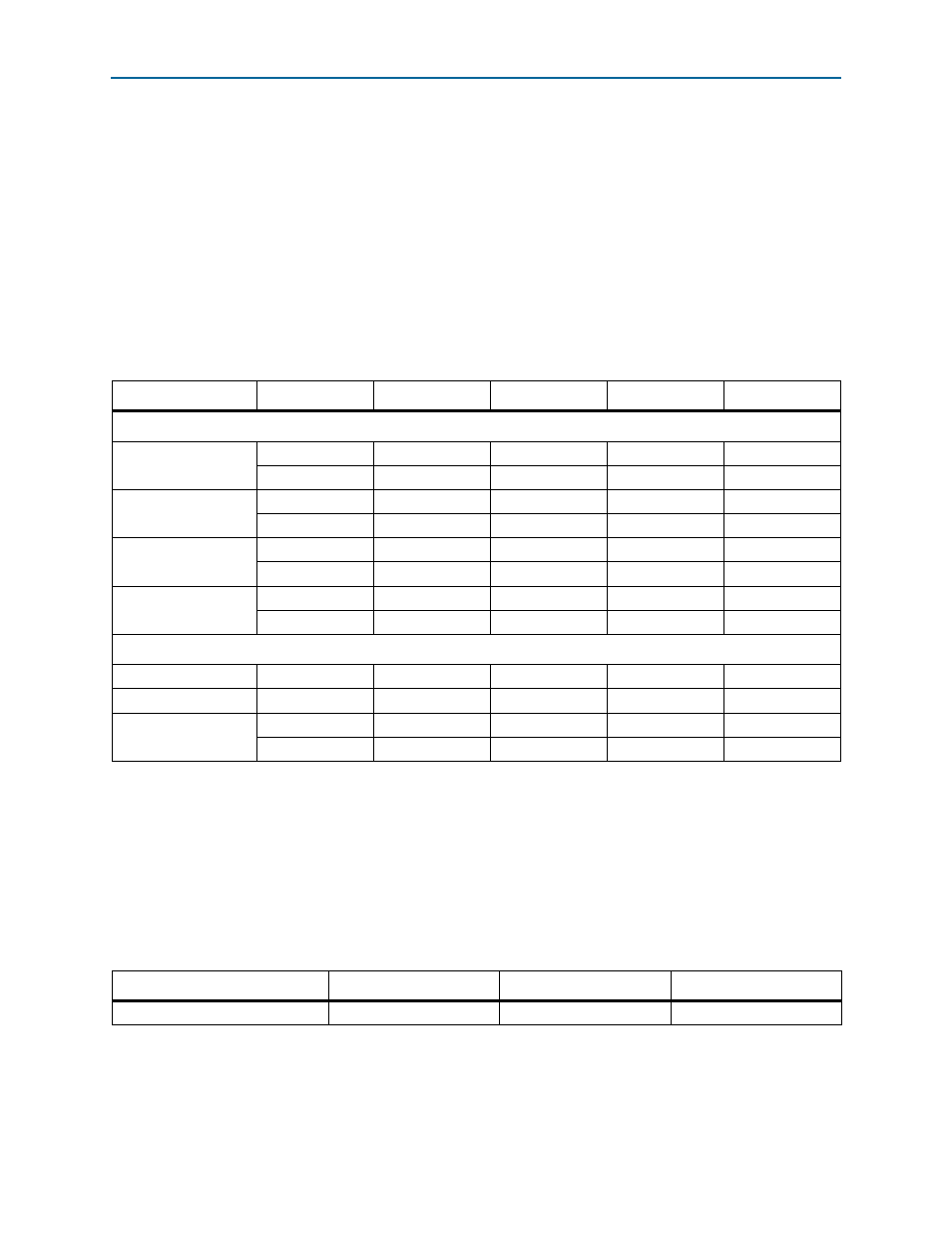

Table 1–5. Hard IP Configurations for the IP Compiler for PCI Express in Quartus II Software Version 11.0

Device

Link Rate (Gbps)

×1

×2

×4

×8

Avalon Streaming (Avalon-ST) Interface

Arria II GX

2.5

yes

no

yes

5.0

no

no

no

no

Arria II GZ

2.5

yes

no

yes

5.0

yes

no

no

Cyclone IV GX

2.5

yes

yes

yes

no

5.0

no

no

no

no

Stratix IV GX

2.5

yes

no

yes

yes

5.0

yes

no

yes

yes

Avalon-MM Interface using Qsys Design Flow

Arria II GX

2.5

yes

no

yes

no

Cyclone IV GX

2.5

yes

yes

yes

no

Stratix IV GX

2.5

yes

no

yes

yes

5.0

yes

no

yes

no

Notes to

(1) For devices that do not offer a ×2 initial configuration, you can use a ×4 configuration with the upper two lanes left unconnected at the device

pins. The link will negotiate to ×2 if the attached device is ×2 native or capable of negotiating to ×2.

(2) The ×8 support uses a 128-bit bus at 125 MHz.

(3) The Qsys design flow supports the generation of endpoint variations only.

Table 1–6. IP Compiler for PCI Express Buffer and Payload Information (Part 1 of 2)

Devices Family

Total RX Buffer Space

Retry Buffer

Max Payload Size

Arria II GX

4 KBytes

2 KBytes

256 Bytes