Avalon-mm application interface – Altera IP Compiler for PCI Express User Manual

Page 129

Chapter 5: IP Core Interfaces

5–43

Avalon-MM Application Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Avalon-MM Application Interface

In the Qsys design flow, only the hard IP implementation is available. In both design

flows, the hard IP implementation is available as a full-featured endpoint or a

completer-only single dword endpoint.

cpl_err[6:0]

(continued)

■

cpl_err[6]

: Log header. When asserted, logs err_desc_func0 header.

Used in both the soft IP and hard IP implementations of the IP core that use

the Avalon-ST interface.

When asserted, the TLP header is logged in the AER header log register if it is

the first error detected. When used, this signal should be asserted at the same

time as the corresponding cpl_err error bit (2, 3, 4, or 5).

In the soft IP implementation, the application presents the TLP header to the

IP core on the err_desc_func0 bus. In the hard IP implementation, the

application presents the header to the IP core by writing the following values

to 4 registers via LMI before asserting cpl_err[6]:

■

lmi_addr: 12'h81C, lmi_din: err_desc_func0[127:96]

■

lmi_addr: 12'h820, lmi_din: err_desc_func0[95:64]

■

lmi_addr: 12'h824, lmi_din: err_desc_func0[63:32]

■

lmi_addr: 12'h828, lmi_din: err_desc_func0[31:0]

Refer to the

“LMI Signals—Hard IP Implementation” on page 5–37

for more

information about LMI signalling.

For the ×8 soft IP, only bits [3:1] of cpl_err are available. For the ×1, ×4 soft IP

implementation and all widths of the hard IP implementation, all bits are

available.

err_desc_func0

[127:0]

I

TLP Header corresponding to a cpl_err. Logged by the IP core when

cpl_err[6]

is asserted. This signal is only available for the ×1 and ×4 soft IP

implementation. In the hard IP implementation, this information can be written to

the AER header log register through the LMI interface. If AER is not implemented

in your variation this bus should be tied to all 0’s.

The dword header[3:0] order in err_desc_func0 is {header0, header1, header2,

header3}.

cpl_pending

I

Completion pending. The application layer must assert this signal when a master

block is waiting for completion, for example, when a transaction is pending. If

this signal is asserted and low power mode is requested, the IP core waits for the

deassertion of this signal before transitioning into low-power state.

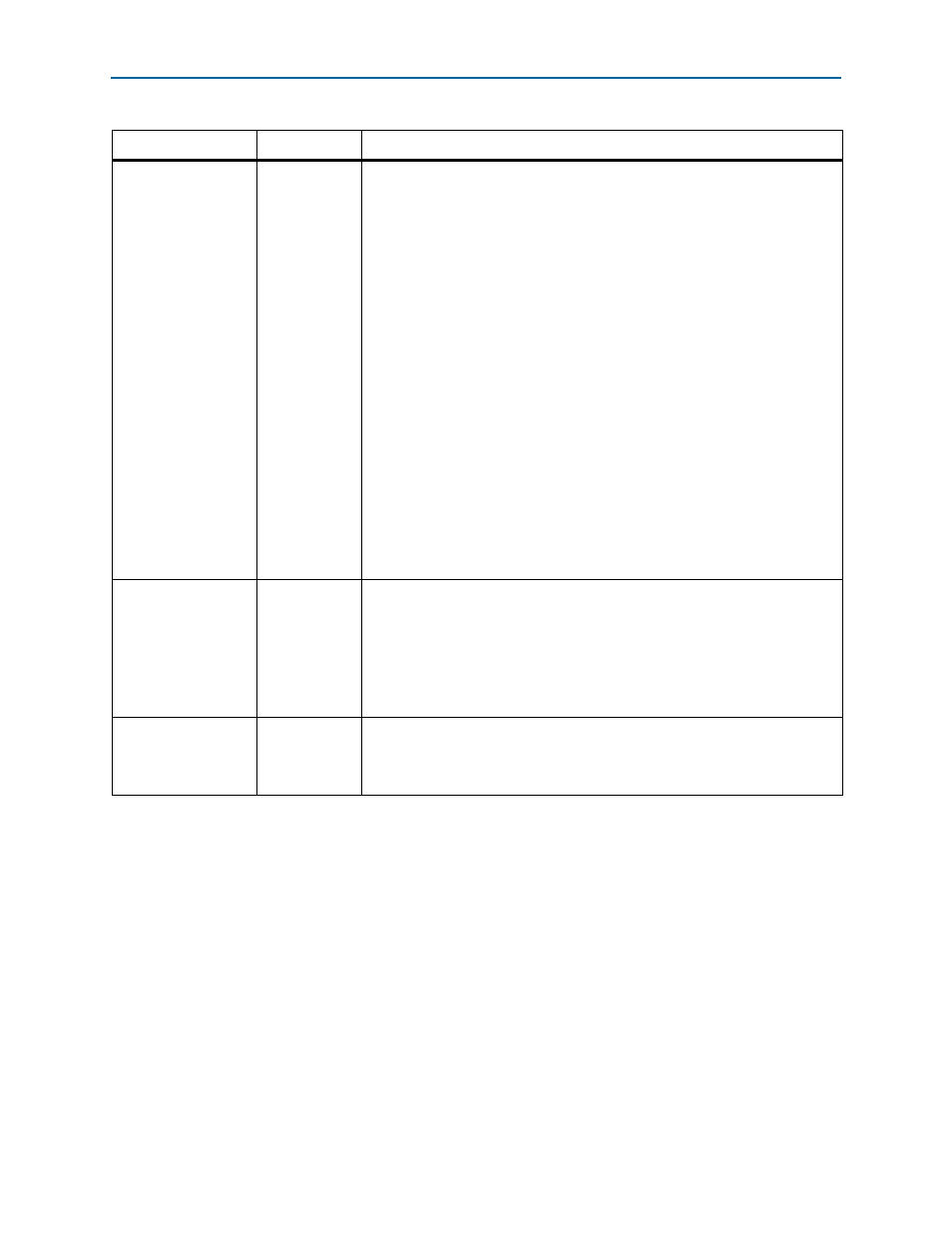

Table 5–21. Completion Signals for the Avalon-ST Interface (Part 2 of 2)

Signal

I/O

Description